ResearchGate Impact Factor (2018): 0.28 | SJIF (2018): 7.426

# Reduction of Leakage Current in CMOS Circuits

Dr S Rooban<sup>1</sup>, Ch Silas<sup>2</sup>, N Venkaiah<sup>3</sup>, Shaik Karishma<sup>4</sup>

Abstract: The leakage control dispersal has gotten one of most testing issue and going up against issue in low power vlsi circuit plan especially with on-chip contraptions as it copies for ordinary interims. The cutting back of point of confinement voltage had accepted the noteworthy activity towards increase in subthreshold leakage current there by making the static (leakage)control dissemination exceptionally high and all out power scattering may fundamentally be contributed by leakage control dispersal. The current work is identified with which we can stop the leakage of current up to a degree by utilizing tired attendant system. Sleepy Keeper utilizes sleep transistors and two extra transistors to lessen the power during sleep mode the control when the battery activity gadgets with length time fluctuation as indicated by backup mode might be depleted out quickly the to the leakage control. A complete report is investigation of different leakage control limiting procedures have been introduced in this paper. The present zone of study and its relating investigation are essentially centered around circuit capacity of execution parameters of tired Keeper. Anyway, for applications invests most span of energy in sleep or backup mode with superior Sleepy Keeper will give another period to vlsi configuration in the case of leakage control decrease.

Keywords: sleepy keeper, power dissipation, threshold voltage

## 1. Introduction

With late types of progress in semiconductor advancement the thickness of transistors in Integrated Circuits continues being building up, that continuously demands pricy cooling and packaging propels. Tolerating this as essential factor, the stock voltages are diminished for lessening the exchanging power scattering. In addition, the limit voltage is likewise downsized for the deterministic presentation. Be that as it may, the scaling component of edge voltage came about in sequently increment of sub threshold leakage current causing leakage (static) control dispersal. Static control scattering is presently developing at a rate corresponding in the exchanging dynamic control dissemination over the profound submicron innovations and battery-worked gadgets the more drawn out the battery endures, the better the leakage control reserve funds. Static control scattering is essentially on account of departure current parts streaming inside the CMOS intersection transistor or CMOS circuits once there's no activity performed on that all through inactive mode. The expecting that leakage power can augment on various occasions per device. The rule of leakage current in a CMOS transistor are:

- 1) Reverse-biased junction leakage current

- 2) Gate induced drain leakage

- 3) Gate direct-tunnelling leakage

- 4) Sub threshold leakage current.

### 2. Previous Methods

#### a) Dual Stack Technique

In Dual stack procedure (Fig 1), 2 PMOS in the draw down system and 2 NMOS in the draw up arrange are utilized. The favoured position is that NMOS taints the high method of reasoning level while PMOS spoils the low basis level. Stood out from past frameworks it requires increasingly essential power defer thing. The deferral is in like manner extended

#### b) Dual Sleep Technique

Double Sleep framework (Fig 2) uses the upside of using the two extra draw up and two extra draw down transistors in rest mode either in OFF state or in ON state. Since the twofold rest bit can be made essential to all reason equipment, a smaller number of transistors is required to apply a particular circuit

Figure 1: Dual Stack Figure 2: Dual sleep

#### c) Sleepy Stack Technique

Right when stack sway is adeptly mixed in with the rest transistor technique the worn-out stack methodology is made (Fig 3). The dormant stack technique segments existing transistors into two half-length transistors utilizing the stack sway. By then rest transistors are related in parallel to one of the disconnected transistors. During rest mode, rest transistors are murdered and stacked transistors smother leakage current while saving state. Power concede thing discipline is a basic issue for this system since every transistor is replaced by three transistors

Figure 3: Sleepy stack

Volume 9 Issue 2, February 2020 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY

Paper ID: ART20204552

DOI: 10.21275/ART20204552

## 3. Proposed Technique

#### transistor is ON.

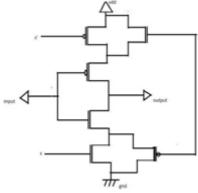

#### a) Sleepy Keeper

Sleepy Keeper method comprise extra NMOS transistor is set in parallel to the draw up rest transistor interfacing VDD to the draw up arrange as appeared in fig. when the rest mode is going on, since the rest transistor is off, this NMOS transistor is the main wellspring of VDD to the draw up organize. An extra single PMOS transistor is put in parallel to the draw down rest transistor which will end up being the main wellspring of Ground to the destroy down system To keep up an estimation of 0 or 1 in rest mode, gave that 0 or 1 worth has just been determined, this methodology utilizes a yield estimation of 0 or 1 for the PMOS transistor associated with GND so that to keep up yield esteem equivalent to 0 or NMOS transistor associated with VDD to keep up yield esteem equivalent to 1 separately in rest mode surrendered (Fig.4).

Figure 4: Sleepy keeper

Sub Threshold leakage current the channel source current of a contrasting transistor works in weak inversion locale is known as subthreshold leakage current. The scattering of current in minority transporters of the channel for a MOS contraption causes the leakage.

### b) Leakage reduction techniques

There are numerous leakage control decrease methods dependent on methods of activity of frameworks. The two activity modes are

- Active mode

- Idle mode.

A large portion of the strategies point if there should be an occurrence of intensity decrease by shutting down the power supply to the circuit during save mode.

### c) Dual threshold CMOS

This strategy use high-limit voltage transistors on to the nonbasic ways to diminish the leakage sum and to keep up circuit execution on basic way that includes the low-edge transistors are utilized. This methodology required for a calculation that find for the door where the high-edge voltage gadget will be contributed. This procedure has been for the most part known as Dual Vth CMOS. In Dynamic Threshold CMOS, the passage and body by each transistor are united with the goal that the leakage is steady low, when the transistor is OFF. The present will be reasonable high if the

### d) Variable threshold CMOS(VTMOS)

This system includes dynamic method for altering the voltage during dynamic mode, which is known as backup control decrease. In this technique the edge voltage Vth is raised during the backup mode by associating the substrate voltage either lower than (for N transistors) or higher than ground (for P transistors). The significant disadvantage of this strategy is that it requires an extra power supply, which may not be proper in some business plans.

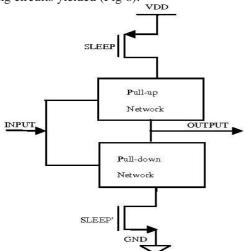

#### e) Power gate - Multi threshold CMOS

In Multi CMOS, a SLEEP transistor is encircled by embeddings high point of confinement contraptions in course of action with low edge transistors between the power supply and ground as showed up in fig. During dynamic mode the rest transistors district unit turned ON, so the standard movement isn't affected as there's a route between the openness and likewise the ground in (Fig 5). For possible later use mode the rest transistors are killed in this way closing down this is known as SLEEP TRANSISTOR.

Figure 5: Power gating (F). Super cut off CMOS:

A technique known as Super Cut CMOS command like MTCMOS gating showed up in fig.6.In this arrangement, during the reinforcement mode, Vgs of the rest transistors are over-driven (PMOS) or under-driven (NMOS) and henceforth this overdriven instrument can bolster the stay by current level. The inter sleeping segment of transistor is that the rest transistors have low edge voltage that can't avoid being that proportionate to that of organized reason circuit. low Vth ensures quick the movement of the method of reasoning circuits yielded (Fig 6).

Figure 6: Basic cut off circuit (G). Transistor stacking:

Volume 9 Issue 2, February 2020 www.ijsr.net

Licensed Under Creative Commons Attribution CC BY

## International Journal of Science and Research (IJSR) ISSN: 2319-7064 ResearchGate Impact Factor (2018): 0.28 | SJIF (2018): 7.426

Transistor stacking is strategy which is actualized unmistakably in powerful mode for leakage current lessening. The leakage current continuously decay when in any event two game plan transistors are put off, which is known as Stack impact or Self-Reverse tendency influence. The hang up of sub edge current will be misused by the transistor stack influence and an improvement in the source voltage Vs of the transistor diminishes as far as possible leakage current thusly. Colossal factor of leakage control sparing can be gotten by developing the measure of transistors related in stack structure. For circuits with no stacking structure, constrained stack can be executed. In compelled stacking, the single transistor's width W can be replaced by two transistors of width W/2 each as showed up in (Fig 7). This results in two transistors killing all the while diminishing leakage current

Figure 7: Transistor stacking (H). Input vector control

The solid reliance of leakage control esteems the concept of transistor stacking is provided on the input merging by referring to the 2-input NAND door example.

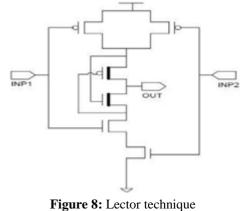

# f) Lector – Leakage Control Transistors:

Two leakage control transistors (PMOS and NMOS) are presented in this strategy between the drawing system and drawing system appears in fig within the rationale circuit. These transistors are connected so that one of the transistors is constantly close to the cut-off voltage for any information mix. This expands the way opposition from supply to ground, prompting huge decrease of leakage flows.

4. Simulation Methodology

The circuit execution parameters, for example, control dissemination; delay, Power Delay Product and region for a portion of the leakage decrease strategies examined above are broke down and organized in table. The points of intesleep and drawbacks of a portion of the leakage decrease

methods are likewise exhibited in a table.

| Technique    | Power saving mode | Delay value(ps) |

|--------------|-------------------|-----------------|

| Lector-100nm | 30.21%            | 18.78           |

| Lector -70nm | 35.13%            | 21.41           |

|                                     |                                                          | <b>D</b> : 4                                            |

|-------------------------------------|----------------------------------------------------------|---------------------------------------------------------|

| Technique                           | Advantages                                               | Disadvantages                                           |

| Force<br>stacking                   | Easy to build,                                           | The rise in the propagation delay                       |

| Sleepy stack<br>Technique           | Less time compared<br>with forced stacking               | Control module<br>for the sleep<br>transistor is needed |

| Input vector<br>control (IVC)       | High power<br>consumption relative<br>to forced stacking | The control system<br>is very complex                   |

| Power gate<br>with stacking         | More leakage<br>savings in both<br>operating mode        | Delay rise                                              |

| Power gating<br>with PMOS<br>& NMOS | Huge power<br>saving, it is mostly<br>chosen method      | Control circuit<br>is essential                         |

| SCCMOS<br>with PMOS &<br>NMOS       | Best in saving<br>of power,<br>easy to construct         | Control circuit<br>is essential                         |

| Lector<br>technique                 | Control circuit<br>is not essential                      | Sleep duration<br>is less                               |

# 5. Results and Simulation

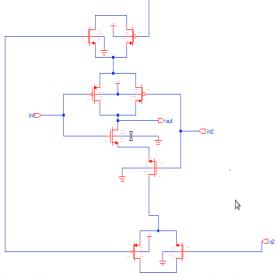

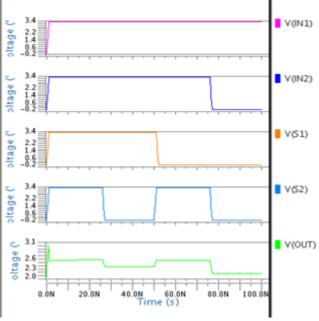

Figure 9: Sleepy keeper using not gate

Figure 10: Sleepy keeper circuit simulation in mentor graphics

Volume 9 Issue 2, February 2020 www.ijsr.net

Licensed Under Creative Commons Attribution CC BY

Figure 11: Output and Waveforms

# 6. Conclusion

The reduction of run power takes on a key role in low-power VLSI circuit designs. Reducing various parameters of the gadget and giving parameters to rising the exhibition of VLSI systems has contributed supplementary to the ascent in run control scattering. this examination gives partner degree appropriate choice to run control step-down strategy for a specific application by a VLSI circuit designer bolstered progressive systematic methodology. The end for that is the essential execution parameters like unique power, run control, spread deferral and the PDP are intensely put down associated. Improving The parameter needed to share 3 optional parameters. The LECTOR method makes it easier to use in any dynamic mode and event backup method. Snappy circuit operation looks like the LECTOR process, if there is a lag, that is the main criteria. For circuit backup mode, SCCMOS is suitable and rendered stacking is suitable for method of dynamic operation. All over-referenced rundown structures are important to the circuit's rate of deliberation. In the coming years, newly rising run control decrease strategies at square level AND door level deliberations are expected to yield additional savings compared to the current circuit level methods.

# References

- [1] Global Semiconductor Research Roadmap (ITRS05).

- [2] S. C. Prasad, K. Roy, "VLSI circuit design with lowpower CMOS." NY: Wiley, 2000, ch. 5, pages 214-219.

- [3] V.S. Deepak subramanyan and Adrain Nunez, "Optical CMOS Digital Circuits Subthreshold Leak Review," in Proc. Thirteenth VLSI Symp National Aeronautics and Space Development. Pp.1-7, 2007.

- [4] Assaderaghi, F., Sinitski, D., Parke, S.A., Borkar, J., Ko, P.K. And Hu, C., "Dynaminingc MOSFET (DTMOS) threshold voltage for VLSI ultra-low voltage," IEEE Lepton Systems group action, Vol. 44,No. 3, August 1997,pp. 414-422

- [5] Johnson, M. De, V., Wei, L., Chen, Z. And Roy, K., "Twin Threshold CMOS Circuits Development and Optimization of Low Voltage High Efficiency," Thirtyfifth design Automation Conference (DAC), 1998, pp. 489-494.

- [6] Kawaguchi, H., Sakurai, T., Nose, K. "The zero.5-V Super Cut-Off CMOS (SCCMOS) give Voltage with Pico ampere Stand-by Current," IEEE Journal of Solid State Circuits vol.35,n.10, Oct 2000, pp.1498-1501.

# **Author Profile**

**S Rooban,** Associate Professor, Department of E.C.E, KL University, Vaddeswaram

**CH Silas,** 160040144, Department of E.C.E, KL University, Vaddeswaram

Neeli Venkaiah, 160040626, Department of E.C.E., KL University, Vaddeswaram

Shaik Karishma, 160040818, Department of E.C.E, KL University, Vaddeswaram

## Volume 9 Issue 2, February 2020 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY