# A Novel Approach towards Bridgeless Converter based SMPS for Power Quality Improvement

#### Pavitra S Bhusaraddi<sup>1</sup>, Dr. Ashok Kusagur<sup>2</sup>

<sup>1</sup>PG Student, Department of EEE, University of BDT College of Engineering, Davangere-577004, India

<sup>2</sup> HOD and Associate Professor, Department of EEE, University of BDT College of Engineering, Davangere-577004, India

Abstract: The conventional SMPS used in computer & other similar appliances has major issues in supplied power on distorted input current, harmonic rich, poor power quality etc. To mitigate these issues, bridgeless SEPIC converter was proposed which provides stiffly regulated output dc voltage even under input/load voltage variations. So that harmonics at the input side was reduced. Model was developed in MATLAB/ Sim power systems. The superior results demonstrated by the proposed model.

Keywords: Bridgeless converter, PFC, SMPS, PCC, PWM, DBR

#### 1. Introduction

Personal computer is one of the electronic equipment which is severely affected by power quality problems. Single stage and two stage conversion of ac voltage into dc voltage have been used in computers to maintain harmonic content within limits and also to obtain stiffly regulated output. Many electronic appliances powered up from the utility utilize the classical method of ac-dc rectification which involves a diode bridge rectifier (DBR) followed by a large electrolytic capacitor. The uncontrolled charging and discharging of this capacitor instigates a harmonic rich current being drawn from the utility. Modern ac-dc converters incorporate power factor correction (PFC) and harmonic current reduction at the point of common coupling (PCC) which improves voltage regulation and efficiency at the load end.

Single stage power conversion is simple, compact and cost effective. However, it suffers from poor dynamic response, high capacitance value and high component stress. So, two stage conversion of ac voltage into multiple dc voltages is mostly preferred in computers [6]. It provides better output voltage regulation, fast dynamic response and blocks the 100Hz component in the first stage itself so that large capacitors at the output side are avoided.

A boost converter is the common choice for providing PFC in power supplies. However, it is not the preferred choice in computer power supplies due to its large input voltage range. The output voltage of a boost converter cannot be controlled to a value less than 300V for a 220V ac input supply. Therefore, buck-boost converter is preferred in computers where wide variations in input voltages and load are expected.

The efficiency of a two stage SMPS is lower than the conventional SMPS, to eliminate this disadvantage, a new bridgeless front end converter is proposed in this paper for computer power supplies and other similar appliances. The elimination of DBR at the front end results in reduced conduction losses and large output voltage range with enhanced efficiency. At the output of the front end converter,

a half bridge converter is used which provides isolation, regulation and multiple dc outputs .The half bridge converter is a common choice because it offers better core utilization.

#### 2. Proposed Work

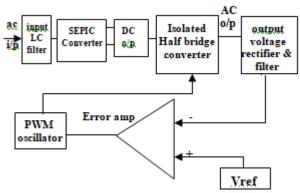

Figure 1: Block diagram for proposed work

Fig 1 shows block diagram for proposed work. The proposed PFC Converter consists of mainly two parts, bridgeless front end ac-dc converter and multi-output isolated dc-dc converter. The front end converter is designed in discontinuous conduction mode (DCM) for achieving inherent PFC while the isolated converter is designed in continuous conduction mode(CCM).

The configuration of proposed PFC converter SMPS with dc output voltage is shown in Fig 2. At the input side, DBR is eliminated by using two SEPICs. The upper converter operates in the positive half cycle and the lower one in the negative half cycle of the input ac voltage. The switching frequency of both the converters is set at 20kHz for efficient control. The design of output inductors for both the converters is carried out in DCM to reduce the complexity in control. The regulation of the output voltage is able to take care of wide variations in the input voltage and load.

The output dc voltage is sensed and compared with a reference voltage from which the voltage error is obtained which is given to a proportional and integral (PI) controller; the PI controller output is compared with a high frequency

## Volume 7 Issue 5, May 2018 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY

saw-tooth wave to yield PWM pulses that are given to both switches simultaneously.

The width of these PWM pulses varies according to the output of the PI controller so that the output dc voltage is regulated effectively which is, in turn, fed to the isolated half bridge converter in the second stage to obtain regulated output voltage. The isolated converter is operated in CCM to take the advantage of reduced stress. If the load in any of the winding changes, the duty cycle changes accordingly to ensure regulated dc outputs.

# 3. Operating Principle

During the positive half cycle of the input voltage, the upper SEPIC operates, in the same way, during negative half cycle the lower SEPIC would operate. The operation of the SEPIC in one PWM cycle is described with the help of the following modes: In the first mode, the high frequency switch Sp turns on, the input inductor Lp1 starts storing the energy which is transferred from the single phase ac mains. Diode Dp1 completes the current path. In the second mode, Sp is turned off and diode Dp2 starts conducting. The energy in output inductor Lp2 starts decreasing to zero in . In the last switching state, the current in the output inductor remains zero until the start of next switching cycle. This mode ensures the DCM operation.

Two high frequency switches are turned on and off alternately in one switching cycle. So, the operation of the converter in one half of the switching cycle is the same as that of the other half cycle.

### 4. Simulation Model

The model is implemented and designed as per the above block diagram. In MATLAB Library, we had selected sinusoidal AC voltage source is selected to provide the voltage to the circuit. To reduce the higher order harmonics, an L-C filter is used at the input side. The chopped AC voltage is converted into DC with the help of diodes used in the SEPIC converter.

Figure 2: Schematic diagram of PFC converter based SMPS

In the first half cycle, the upper switch S1 is turned on. The diodes on the secondary side start conducting and the inductors in all the secondary windings start storing energy. All the filter capacitors discharge through the loads to maintain dc output voltages as constants. In the next half cycle of the PWM period, the upper switch is turned off. The secondary diodes are turned on to free-wheel the inductors currents.

# Design of the proposed bridgeless converter based SMPS System

The design for the positive half cycle operated PFC converter is carried out here. The negative half cycle operated converter is designed in the same way. The average voltage Vacav is calculated as,

V acav =

$$\frac{2\sqrt{2} \times \text{Vac}}{\pi} = \frac{2\sqrt{2} \times 250\text{V}}{3.14} = 225\text{V}.....(1)$$

The duty cycle D of the PFC buck-boost converter is expressed as the ratio of its output dc voltage to the sum of output dc voltage and input voltage.

Duty cycle,

$$D = \frac{VPFC}{VPFC + Vacav}$$

....(2)

The input inductor value is calculated for the permitted ripple of 40% of input current.

where, f is the switching frequency of the PFC converter

The equivalent value of inductance of the PFC converter is given as,

Where, Ka is critical conduction parameter

The output inductor value is calculated as,

The intermediate capacitor value is estimated as,

$$Cp = \frac{1}{(\omega r)^2 (Lp1 + Lp2)}$$

.....(6)

Where  $\omega_r$  is the angular frequency ( $\omega_r = 2\pi fr$ )

#### **Specifications:**

| Frequency                        | 50Hz   |

|----------------------------------|--------|

| Switching frequency              | 20kHz  |

| Input inductors (Lp1, Ln1)       | 4.35mH |

| Output inductors (Lp2, Ln2)      | 225µH  |

| Intermediate capacitors (Cp, Cn) | 0.22µF |

| Output voltage                   | 5Vdc   |

### 5. Results & Discussions

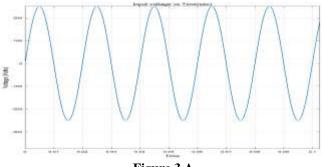

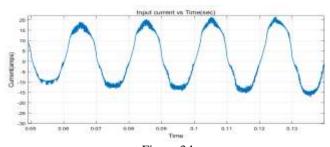

Figure 3 A

Figure 3 b Figure 3: Input voltage and current of PFC power supply at rated condition

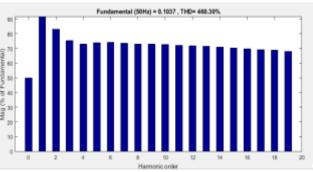

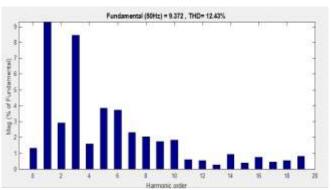

Figure 4: Harmonic spectrum of conventional SMPS

Figure 5: Harmonic spectrum of PFC converter based MPS

Table 1: THD Comparison

| Parameters         | Conventional<br>SMPS | PFC converter<br>based SMPS |

|--------------------|----------------------|-----------------------------|

| Input line current | 460.30%              | 12.43%                      |

| Input voltage      | 24.89%               | 0.01%                       |

From fig 3, the input ac voltage and current are found to be sinusoidal. So there is no harmonics at the input side, thus power quality is improved. From fig 4 & fig 5, we can observe that harmonic distortion is reduced to 12.42%. The comparison is shown in table 1. The output voltages are maintained constant with their respective output currents.

### 6. Conclusion

In this bridgeless SEPIC Converter based Switch Mode Power Supply were implemented. SEPIC converter is used to reduce the harmonics and to get stiffly regulated output. The proposed scheme was implemented in MATLAB/ SimPowerSystem, the results are achieved experimentally.

DOI: 10.21275/ART20182629

#### References

- D. O. Koval and C. Carter, "Power quality characteristics of computer loads," IEEE Trans. on Industry Applications, vol. 33, no. 3, pp. 613-621, May/June1997.

- [2] H Veeresh, Ashok Kusagur, "ZCS/ZVS push pull DC/DC converter" IJLTEMAS,vol 04 pp-73-79, Jan 2015,ISSN 2278-2540.

- [3] B. Singh, B.N. Singh, A. Chandra, K. Al-Haddad, A. Pandey and D.P. Kothari, "A review of single-phase improved power quality AC-DC converters" IEEE Trans. on Industrial Electronics, vol.50, no.5, pp.962-981, Oct. 2003.

- [4] K. Mino, H. Matsumoto, Y. Nemoto, S. Fujita, D. Kawasaki, RyujiYamada, and N. Tawada, "A front-end converter with high reliability and high efficiency," in IEEE Conf. on Energy Conversion Congress and Exposition (ECCE),2010, pp. 3216-3223.

- [5] Jih-Sheng Lai, D. Hurst and T. Key, "Switch-mode supply power factor improvement via harmonic elimination methods," in 6th Annual IEEE Proc. on Applied Power Electronics Conference and Exposition.

- [6] C. A. Gallo, F. L. Tofoli and J. A. C. Pinto, "Two-stage isolated switch mode power supply with high efficiency and high input power factor," IEEE Trans. on Industrial Electronics, vol. 57, no. 11, pp. 3754-3766, NOV. 2010.

- [7] S. N. Padhy and S. Kalra "A high performance bridgeless AC-DC-DC power factor corrector for LED driver application," in Annual IEEEConf. on India Conference (INDICON), 2013, pp. 1-6.

- [8] A. A. Fardoun, E.H. Ismail, A. J. Sabzali and M.A. Al-Saffar, "New efficient bridgeless Cuk rectifiers for PFC applications," IEEE Trans. On Power Electronics, vol. 27, no. 7, pp. 3292-3301, July 2012.

- [9] A. J. Sabzali, E. H. Ismail, M. A. Al-Saffar and A. A. Fardoun, "New bridgeless DCM Sepic and Cuk PFC rectifiers with low conduction and switching losses," IEEE Trans. on Industry Applications, vol. 47, no. 2, March/April 2011, pp. 873-881.

- [10] Abraham I. Pressman, Keith Billings and Taylor Morey, "Switching Power Supply Design," 3rd ed., McGraw Hill, New York, 2009

- [11] V Hulugappa, A Kusagur, "Comparative analysis of DC-DC converter topologies with soft-switching techniques" ICEECCOT,016 International conference on 9-10 Dec 2016

- [12] Manjunath,T G, Kiusagur, Ashok, "Fault Diagnosis and Reconfiguration of a Multilevel Inverter Switch Failure-A Performance Perspective" International Journal of Electrical and Computer Engineering; Yogyakarta Vol.6, Iss. 6, (Dec 2016): 2610-2620

- [13] Ashok Kusagur, Optical Choice & Allocation of Facts Devices for Congestion management in Deregulated Power System using GA, Emerging Research Library(EPL) 5(4), 188-195, 2014.

- [14] A. J. Perin and I. Barbi, "A new isolated half-bridge soft-switching pulse-width modulated DC-DC converter," in *Seventh Annual IEEE Conf.* on *Applied*

*Power Electronics Conference and Exposition, APEC*'92, 1992, pp. 66-72.

[15] Hong Mao, J. Abu-Qahouq, Shiguo Luo and I. Batarseh, "Zero-voltageswitching half-bridge DC-DC converter with modifiedPWM control method," *IEEE Trans.* on *Power Electronics*, vol.19,no. 4, pp.947-958, July 2004.

DOI: 10.21275/ART20182629