# Developing a Scheme that Reduces the Protection Liability

## Bonala Srinath<sup>1</sup>, G. Purna Chender Rao<sup>2</sup>

<sup>1</sup>M. Tech Student, ECE, SVS Group of Institutions, Telangana, India

<sup>2</sup>Assistant Professor, ECE, SVS Group of Institutions, Telangana, India

Abstract: An average illustration of individuals elements are digital filters. The rise in complexity also poses reliability challenges and produces the requirement for fault-tolerant implementations. A plan according to error correction coding continues to be lately suggested to safeguard parallel filters. Because the complexity of communications and signal processing systems increases, the same is true the amount of blocks or elements they have. Oftentimes, a number of individuals elements be employed in parallel, carrying out exactly the same processing on several signals. the suggested coding plan is presented and highlighted having a couple of practical situation studies. For the reason that plan, each filter is treated like a bit, and redundant filters that behave as parity check bits are brought to identify and proper errors. Within this brief, the thought of using coding strategies to safeguard parallel filters is addressed inside a more general way. Particularly, it's proven that the truth that filter inputs and outputs aren't bits but figures allows a far more efficient protection. Finally, both effectiveness in safeguarding against errors and also the cost are evaluated for any field-per-sellable gate array implementation. This cuts down on the protection overhead and makes the amount of redundant filters in addition to the quantity of parallel filters. The suggested plan is first described after which highlighted with two situation studies. When a number of individual's inspections fail, a mistake is detected. Our desire response could be infinite or perhaps be nonzero for any finite quantity of samples. Within the first situation, the filter is definitely an infinite impulse-response (IIR) filter, as well as in the 2nd, the filter is really a finite impulse-response (FIR) filter.

Keywords: Coding, parallel filters, soft errors

#### 1. Introduction

This parallel operation could be used for fault tolerance. Parallel filters are generally present in modern signal processing and communication systems. Oftentimes, filters carry out the same processing on several incoming signals as there's a inclination to make use of multiple-input-multiple output systems. Actually, reliability is really a major challenge for electronic systems. Particularly, soft errors are an essential issue, and lots of techniques happen to be suggested through the years to mitigate them. A few of these and techniques customize the low-level design implementation from the integrated circuits to avoid soft errors from occurring. Other techniques work on a greater abstraction level with the addition of redundancy that may identify and proper errors. One classical example is using triple modular redundancy (TMR) where the design is tripled along with a majority election from the outputs are utilized to correct errors. Another example is using error correction codes (ECCs) to safeguard the bits kept in memory products [1]. Within this situation, numerous parity inspections are calculated and kept in the memory to ensure that errors could be detected and remedied once the data are read. Finally, for programs which have regular structure and qualities, individuals could be used to identify and proper errors having a less expensive than TMR. This is actually the situation for a lot of signal processing circuits. Oftentimes, ECCs or specific protection techniques are coupled with TMR to attain an entire protection. For instance, the ECC encoders and decoders might be protected with TMR to make sure that they aren't impacted by errors. In individuals cases, TMR can be used to safeguard a small sector from the circuit that can't be paid by the ECC or even the specific technique. The security of digital filters continues to be broadly analyzed. For instance, fault-tolerant

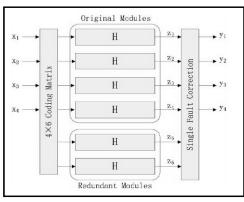

implementations in line with the utilization of residue number systems or arithmetic codes happen to be suggested. Using reduced precision replication or word-level protection continues to be also analyzed. An alternative choice to do error correction is by using two different filter implementations in parallel. All individuals' techniques concentrate on the protection of merely one filter. The security of parallel filters only has been lately considered. A preliminary method to safeguard two parallel filters was suggested. This plan was generalized, where using a plan according to ECCs was presented. Within this work, each filter was treated like a bit with an ECC, and extra filters are put into behave as parity check bits. Which means that, for single error correction, the amount of redundant filters needed is equivalent to the amount of bits necessary for a conventional single error correction Hamming code [2]. For instance, for four parallel filters, three redundant filters are needed, whereas for eight filters, four redundant filters are essential. This plan therefore considerably cuts down on the implementation cost in comparison with this of TMR. This brief studies the security of parallel filters using more general coding techniques. Particularly, a vital difference with ECCs is the fact that both filter inputs and outputs are figures. Therefore, not just a zero or perhaps a one can be used as the coding (as completed with ECCs). This is often used, as proven within the relaxation of the brief, to supply error correction with the addition of 3 redundant filters whatever the quantity of parallel filters. The lower quantity of redundant filters has no effect on ale the plan to fix errors but cuts down on the implementation cost. Within the relaxation of the brief, first, the parallel filters and also the existing ECC-based protection plan are described [3]. Then, the suggested coding plan is presented and highlighted having a couple of practical situation studies. Finally, the situation research is evaluated for any field-per-sellable gate

Volume 5 Issue 9, September 2016 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY array (FPGA) implementation and in comparison using the formerly suggested ECC-based technique. The outcomes reveal that using a more general coding plan cuts down on the protection overhead while supplying an identical error correction capacity to that particular from the ECC plan.

Figure 1: Proposed Coding Scheme

## 2. Filter Implementation

In the two cases, the filtering operation is straight line. This property could be used within the situation of parallel filters that work on different incoming signals. When a number of individual's inspections fail, a mistake is detected. Our desire response could be infinite or perhaps be nonzero for any finite quantity of samples. Within the first situation, the filter is definitely an infinite impulse-response (IIR) filter, as well as in the 2nd, the filter is really a finite impulseresponse (FIR) filter. The mistake could be remedied according to which specific inspections unsuccessful. Within this ECC-based plan, the coding from the redundant filters is dependent on simple additions that switch the XOR binary procedures in traditional ECCs. This ECC-based plan cuts down on the protection overhead in comparison by using TMR [4]. The input signals are encoded utilizing a matrix with arbitrary coefficients to create the signals that go into the four original and 2 redundant filters. The mistake correction and recognition logic could be simplified presuming that there's merely a single error remedied by reconstructing the outputs while using remaining filters. For that suggested coding plan to operate, the encoding matrix needs to fulfill some conditions. when a mistake is detected, it may be remedied by recomposing the affected filter output and also the remaining original filter outputs. The 2nd situation study is comparable, but eight filters need to be protected. As one example of using the suggested plan, two situation studies that think about the protection of 4 and eight parallel filters are presented here. In the two cases, a coding matrix that preserves the inputs towards the original filters can be used. The dwelling is equivalent to within the first situation study and thus is the amount of redundant filters as with the suggested plan, it doesn't rely on the amount of filters. This can be a obvious edge on the prior ECC plan where the quantity of redundant filters develops as the amount of filters to safeguard increases [5]. The computational complexity required implementing error recognition and correction within the suggested technique is mainly because of the two redundant filter modules. Another procedure required computing the check vector and proper the errors are simpler, although a little more complex than individuals within the ECC-based plan.

#### 3. Conclusion

The sensible implementation was highlighted with two situation studies which were evaluated to have an FPGA implementation and in comparison having a formerly suggested technique. A brand new approach to implement fault-tolerant parallel filters continues to be presented within this brief. The suggested plan exploits the linearity of filters to apply a mistake correction mechanism. Particularly, two redundant filters whose inputs are straight line mixtures of the initial filter inputs are utilized to identify and look for the errors. Therefore, the suggested technique could be helpful to apply fault tolerant parallel filters. Future work will consider using the plan to parallel filters that have a similar input signal but different impulse reactions. The coding of individuals straight line combinations was formulated like a general problem to then show the way it can efficiently be implemented. That technique depends on using ECCs so that each filter is treated like a bit within the ECC. The outcomes reveal that the suggested plan outperforms the ECC technique.

## References

- M. Nicolaidis, "Design for soft error mitigation," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 3, pp. 405–418, Sep. 2005.

- [2] P. Reviriego, S. Pontarelli, C. Bleakley and J. A. Maestro, "Area efficient concurrent error detection and correction for parallel filters," *IET Electron. Lett.*, vol. 48, no 20, pp. 1258–1260, Sep. 2012.

- [3] B. Shim and N. Shanbhag, "Energy-efficient soft errortolerant digital signal processing," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 14, no. 4, pp. 336–348, Apr. 2006.

- [4] A. Chatterjee, and M. A. d'Abreu, "The design of faulttolerant linear digital state variable systems: Theory and techniques," *IEEE Trans. Comput.*, vol. 42, no. 7, pp. 794–808, Jul. 1993.

- [5] A. Sibille, C. Oestges and A. Zanella, *MIMO: From Theory to Implementation*, New York, NY, USA: Academic, 2010.

Volume 5 Issue 9, September 2016 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY