# Design of Reconfigurable Digital Filter Bank for Hearing Aid

# Sneha Raj<sup>1</sup>, Athira Shaji<sup>2</sup>

<sup>1</sup>Department of ECE, Sree Buddha College of Engineering, Pattoor, Kerala, India

<sup>2</sup>Assistant Professor, Department of ECE,Sree Buddha Collge of Engineering, Pattoor, Kerala, India

Abstract: A hearing aid is an electroacoustic device for improving the hearing ability of hearing impaired. It should be designed such that it is able to adjust the magnitude response of arbitrary input frequencies, have low power consumption for reasonable battery life, output should be provided with a low delay and the overall structure should be small in size. In a simple hearing aid gain is applied to the whole input frequency range, due to which the intensities of some speech sounds after amplification will be larger than the discomfort thresholds. To solve this problem a highly reconfigurable non-uniform digital FIR filter bank structure is proposed, where the whole frequency range is divided into several subbands and each sub band has its own amplification coefficient. The non-uniform spaced sub bands can be realized with variable bandwidth filters. Each VBF can be realized as a combination of arbitrary sample rate converters and FIR filter. The sample rate converters will be implemented using cascaded integrator comb (CIC) filters. The proposed FIR filters will be implemented using distributed arithmetic. This structure will be multiplier less to reduce the resources, thereby allowing for low power consumption. The performance is evaluated using MATLAB.

Keywords: Variable Bandwidth Filters, cascaded integrator comb (CIC) filters, Distributed Arithmetic (DA), MATLAB

### 1. Introduction

A Hearing aid is an electroacoustic device for improving the hearing ability of hearing impaired. More and more people around the world suffer from hearing losses. The increasing average age and the growing population are the main reasons for this. The main task of the hearing aid is to selectively amplify the audio sounds such that the processed sound matches one"s audiogram. An audiogram with frequencies on X-axis and hearing threshold on Y-axis indicates the hearing capabilities of a person for various frequencies. It measures the people"s hearing threshold as a function of frequency. Hearing thresholds become high at certain frequencies which causes hearing loss i.e., they have low hearing sensitivity at certain frequencies. To compensate this type of hearing loss, it is necessary to selectively amplify sounds at required frequencies.A Hearing aid should be designed such that it is possible to adjust the magnitude response of arbitrary input frequencies, have low power consumption for reasonable battery life, output should be provided with a low delay and the overall structure should be small in size.

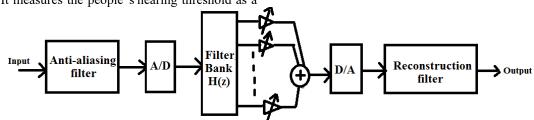

Figure 1: Block diagram of a digital hearing aid

The general working procedure of a digital hearing aid is as follows. The microphone takes the input from the environment which is in analog form. Then A/D converter converts the analog signal into digital form. Then digital filter bank separate input signal into multiple channels each having particular band of frequencies. After that gain is adjusted for required band automatically. Finally D/A converter convert the processed signal into analog form.

Digital filter banks are the inevitable part of signal processing applications such as channelization, spectrum sensing, electroencephalogram classification, loudspeaker equalization, digital hearing aids etc. Also they are used extensively in various wireless communication, audio and signal processing applications. It is desirable for all the emerging applications that the digital filter bank must have linear phase and it should be reconfigurable such that it is possible to control its frequency parameters without reimplementing the hardware. Since filtering is one of the most computationally complex and power consuming task, the design of a digital filter bank which is hardware efficient is a challenging task.

The popular digital filter-bank design approaches are:

1) Velcro approach [1], 2) modulation-based approach [1], [2] and 3) interpolation-based approach [3], [4], [5]. The per-channel filter bank is based on Velcro approach, and it consists of parallel bank of filters such that a distinct filter is used for each sub band [1]. The per-channel approach provides a great deal of flexibilities in the design of nonuniform fixed-filter banks where the sub band bandwidths may not be same but fixed and known in

## International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Index Copernicus Value (2013): 6.14 | Impact Factor (2015): 6.391

advance. However, it is not a hardware-efficient solution owing to the linear increase in complexity with the number of sub bands. In modulation-based filter banks [1], [2], a low pass prototype filter is modulated to obtain multiple band pass responses with distinct center frequencies. Since there is no need of implementing separate filter for each sub band, the modulated filter banks are computationally efficient. Among the existing modulated filter banks, the discrete Fourier transform filter bank (DFTFB) [1] is widely used uniform filter bank, that is, sub band bandwidth is fixed and equal to the pass band width of the prototype filter. The interpolation-approach-based fast filter bank (FFB) [3] is a low-complexity alternative to the DFTFB [1], [2] and is suitable for applications requiring sharp transition bandwidth (TBW). Like DFTFB, the FFB [3] is a uniform filter bank. The modulation and interpolation-based filter banks [1] [2],[3],[4] cannot provide an unabridged and independent control over the bandwidth and the center frequency of each sub bands. This is because, the bandwidth of all sub bands changes simultaneously when the cut-off frequency of the prototype filter is changed. Consequently, the resolution of these filter banks depends on the smallest sub band bandwidth specifications rather than the number of received channels and is very high. The higher the resolution of the filter bank, the higher the area complexity, power consumption, and delay.

The patients cannot improve their specific auditive performance by using limited number of sub bands which are fixed. The filter banks of most of the currently available hearing aids consists of fixed bands. This degrades the flexibility in matching of hearing loss with steeply sloping audiograms. One solution is to use a device with higher number of frequency bands for matching the audiogram with minimum matching error. But increasing the number of bands will subsequently increase the power consumption and also the cost . Therefore it would be beneficial to design a filter structure with less number of bands and which can be easily customized with minimum change in parameters, for any hearing impaired person.

# 2. Proposed System

A new approach of reconfigurable digital filter bank is proposed in this paper which is based on the concept of Variable Bandwidth Filters. The audible frequency range is divided into non-uniform spaced sub bands and are realized using Variable Bandwidth Filters. The filter bank decomposes the input signal into different bands so that the prescribed gains can be applied to compensate the raised hearing thresholds.

Dividing the frequency range uniformly is straightforward approach but it does not consider the unique characteristic of human hearing. Thus non-uniform filter banks that mimic the resolution characteristic of human hearing is proposed in this work. Each VBF can be realized as a combination of two arbitrary sample rate converters and a fixed bandwidth FIR filter. Usually the sample rate converters are realized using ployphase filters which uses multiplier structures causing increased power consumption [8]. The proposed VBF uses cascaded integrator comb filters proposed by Hogenauer [7] which provides an efficient way of performing decimation and interpolation. The advantage of CIC filters is that they are flexible and multiplier free filters suitable for hardware implementations. Thus the sample rate converters can be realized using CIC filters. The proposed FIR filters can be implemented using distributed arithmetic. Since the proposed FIR filters uses distributed arithmetic the overall structure will be multiplier less thereby reducing the resources, thus allowing for low power consumption.

| Table 1. Division of Sub ballus |                     |

|---------------------------------|---------------------|

| Band                            | Frequency range(Hz) |

| 1                               | 0-250               |

| 2                               | 250-500             |

| 3                               | 500-750             |

| 4                               | 750-1000            |

| 5                               | 1000-1500           |

| 6                               | 1500-2000           |

| 7                               | 2000-3000           |

| 8                               | 3000-4000           |

| 9                               | 4000-5000           |

| 10                              | 5000-6000           |

| 11                              | 6000-6500           |

| 12                              | 6500-7000           |

| 13                              | 7000-7250           |

| 14                              | 7250-7500           |

| 15                              | 7500-7750           |

| 16                              | 7750-8000           |

Table 1: Division of Sub bands

Variable bandwidth filter facilitates the reduction and enhancement of the bandwidth without changing the filter order or filter coefficients. This is based on changing the sampling frequency of the input signal [8]. It is accomplished by interpolating/decimating the input series to obtain an intermediate time series at a new sample rate proportional to the required bandwidth. The interpolated/ decimated series are processed by the fixed length FIR filter, now operating at the changed sample rate. The output from the FIR is then decimated/interpolated back to the original input sample rate, which effectively changes the bandwidth. The change in bandwidth of the particular band can be achieved by modifying only the bandwidth ratio given as input to the sample rate converter.

Filter bank the most important functional block in digital hearing aids makes the sound audible for hearing-impaired people. The filter bank decomposes the input signal into different bands so that the prescribed gains can be applied to compensate the raised hearing thresholds. Dividing the frequency range uniformly is straightforward approach but it does not consider the unique characteristic of human hearing. Thus non-uniform filter banks that mimic the resolution characteristic of human hearing is proposed in this work. International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2015): 6.391

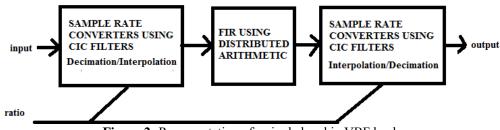

Figure 2: Representation of a single band in VBF bank

#### 2.1 Sample Rate Conversion

The process of conversion of sampling rate of a signal to a new sample rate is called sample rate conversion. The systems that employ multiple sampling rates in the processing of digital signals are called multi rate digital signal processing systems. Sample rate conversion can be achieved by interpolating or decimating the input signal.Interpolation is the process of up sampling followed by filtering. Up sampling is the process of inserting zerovalued samples between the original samples to increasing the sampling rate. The primary reason to interpolate is simply to increase the sampling rate at the output of one system so that it can be the input of another system operating at a higher sampling. The result is a signal at "L" times the original sampling rate which has the same spectrum over the input Nyquist range.Decimation is the reverse process of interpolation. The decimator generates one output for every "M" input samples and the output rate is thus "M" times slower than that of the input sequence.

CIC filters are multirate filters used for realising large sample rate changes in digital systems.CIC filters are multiplier less structures, which contains only adders and delay elements which is a great advantage when aiming at lower power consumption.

#### **2.2 Distributed Arithmetic**

Distributed Arithmetic is a different approach for implementing digital filters. The basic idea is to replace all multiplications and additions by a look up table and a shifter-accumulator.Distributed Arithmetic provides costeffective and area-time efficient computing structures.

For an N<sup>th</sup>-order FIR filter, the generation of each output sample takes N+1 multiply accumulate (MAC) operations. Since multiplication is repeated addition it is the strongest operation. It requires large portion of chip area and hence power consumption is more. Memory-based structures are more regular compared with the multiply accumulate structures and have many advantages such as greater potential for high throughput and reduced-latency implementation..Thus Distributed Arithmetic architecture is a wise choice for FIR.

Distributed Arithmetic (DA) technique is bit-serial in nature. It is actually a bit-level rearrangement of the multiply and accumulation operation. The basic DA is a computational algorithm that affords efficient implementation of the weighted sum of products, or dot product. DA is a bit-serial operation used to compute the inner (dot) product of a constant coefficient vector and an input vector(variable) in a single direct step [9].

$$Y = -X_{k0} A_k 2^0 + \sum_{b=1}^{N-1} 2^{-b} \sum_{k=0}^{K-1} X_{kb} A_k$$

(1)

Where, k is the filter length,  $A_k$  filter coefficients For k=3,N=4,the DA technique pre-computes all possible values of Y.

$\begin{array}{l} Y = -(X_{00}A_{0+}X_{10}A_{1+}X_{20}A_{2})2^{0} + (X_{01}A_{0+}X_{11}A_{1+}X21A2)2^{-1} + \\ (X_{02}A_{0+}X_{12}A_{1+}X22A2)2^{-2} + (X_{03}A_{0+}X_{13}A_{1+}X23A2)2^{-3} \ (2) \\ \mbox{All the possible values are stored in lookup table} \end{array}$

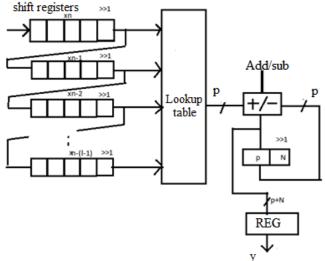

#### 2.3 DA-Based Architecture for Implementing FIR Filter

All the elements of the input vector  $x = [x_0, x_1, \dots, x_{k-1}]$  are stored in "b"bit shift registers. The architecture considers in each cycle the  $b^{th}$  bit of all the elements and concatenates them to form the address to the lookup table (LUT). According to the input values, the LUT provides the pre computed output. The output of the lookup table is given to the shift and add section. For the most significant bits (MSBs) the value in the lookup table is subtracted from a running accumulator and for the rest of the bit locations values from lookup table are added in the accumulator.To cater for weights of different bit locations, in each cycle the accumulator is shifted to the right. To keep space for the shift, the size of the accumulator is set to P + N, where a P bit adder adds the current output of the ROM in the accumulator and N bits of the accumulator are kept to the right side to cater for shift operations. The data is shift to the shift register from LSB. The dot product takes N cycles to compute the summation.

Figure 3: DA based architecture for implementing FIR filter

Volume 5 Issue 7, July 2016 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY The input signal is changed into a new sample rate using the sample rate converter (interpolation/decimation). The output of which is in a parallel form. Since the shift register used in DA architecture is bit serial in nature, the parallel output should be converted into serial form using a parallel to serial converter. The interpolated/decimated series are processed by the DA-FIR and is again decimated/interpolated back to the original sample rate.

## 3. Design Example

Consider the design of a lowpass filter with passband frequency 250 Hz, stopband frequency 1000 Hz Bandwidth : 250 Hz Maximum Pass band ripple: 0.01dB Minimum stop band attenuation: 65dB Sampling frequency: 16 kHz, order N=73

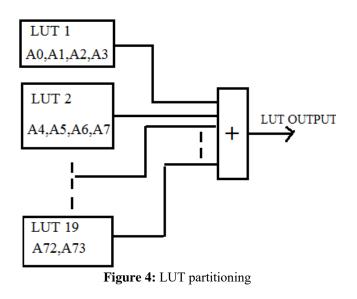

Thus the lookup table must hold the 74 coefficients. Since the low pass filter is of higher order, the size of the LUT will also increase exponentially. This in turn degrades the performance. Thus for higher order filters, LUT should be reduced to a reasonable level. This can be achieved by partitioning of LUTs. Each LUT partition operates on a different set of filter taps.

Fig.4 shows the partitioning of LUT into 19.All the LUTs except the last LUT holds four coefficient values and the last LUT holds two coefficient values. The address lines of the LUT is driven by concatenating the LSB's from the shift registers. According to the input address, LUTs provides the output. The possible input for LUT 1 is 0(0000) - 15(1111). For eg: Input = 1011 means

Output = 1. A0 + 0. A1 + 1. A2 + 1. A3

Likewise LUT provides ouput for all input combinations. The output from all LUTs are added together to form the output corresponding to the 74 bit address from the shift register.

# 4. Results and Discussions

The whole frequency range up to 8 KHz is divided into different sub bands as per TABLE 1.Frequency up to 8 KHz

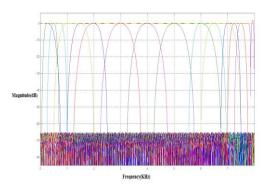

is deemed to be average normal hearing frequency. In this work, more sub bands are provided at low frequencies and high frequencies. Hearing loss occurs mainly at these low and high frequencies. Better performance can be achieved by better distribution of sub bands. The performance is evaluated using MATLAB and the frequency response obtained by combining 16 bands is shown in fig.5. The frequency response is obtained by combining a low pass filter followed by band pass filters and finally a high pass filter bank is that the range of frequencies for which gain is required can be configured according to the requirement of a particular patient.

Figure 5: Frequency response of proposed nonuniform filter bank

# 5. Conclusion and Future Work

A highly re-configurable non-uniform digital FIR filter bank structure has been proposed for the hearing aid application. The use of CIC filters as sample rate converters and Distributed Arithmetic based FIR filters lead to area and power efficient structure for digital filter bank. With increase in the number of sub bands, especially in low and high frequencies, the performance is enhanced. The proposed design can be efficiently implemented on hardware. The future works include the implementation of reconfigurable 16 band non-uniform digital filter bank on a hardware platform such as FPGA.

## References

- [1] L. Pucker, "Channelization techniques for software defined radio," in *Integrated Circuits and Systems.*,USA:Springer-Verlag,2009.

- [2] R. Mahesh and A. P. Vinod, "Reconfigurable discrete Fourier transform Filter banks for variable resolution spectrum sensing," in *Proc. IEEE Int. Conf. Commun. Syst.*, Singapore, Nov. 2010, pp. 483–487.

- [3] K. G. Smitha and A. P. Vinod, "A multi-resolution fast filter bank for spectrum sensing in military radio receivers," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. 20, no. 7, pp. 1323–1327, Jun. 2011.

- [4] S.J.Darak, A. P.Vinod, K. G. Smitha, and E. M.-K. Lai, "Low complexity reconfigurable fast filter bank for multi-standard wireless receivers,"*IEEE Trans. Very Large Scale Integr.(VLSI) Syst.*, vol. 21,no. 6, pp. 1165–1169, Jul. 2012.

Volume 5 Issue 7, July 2016 www.ijsr.net

## Licensed Under Creative Commons Attribution CC BY

- [5] Y. C. Lim and B. Farhang-Boroujeny, "Fast filter bank (FFB)," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 39, no. 5, pp. 316–318, May 1992.

- [6] R. Mahesh and A. P. Vinod, "Low complexity flexible filter banks for uniform and non-uniform channelisation in software radios using coefficient decimation," *IET Circuits, Devices Syst.*, vol. 5, no. 3, pp.232–242, May 2011.

- [7] E.B. Hogenauer, "An economical class of digital filters for decimation and interpolation", *IEEE Trans. Acoust., Speech, Signal Process.*vol.29, no. 2, pp. 155–162, 1981.

- [8] James T George., Elizabeth Elias "A 16-Band Reconfigurable Hearing Aid using Variable Bandwidth Filters" Global Journal of Researches in Engineering, Volume 14 Issue 1 Version 1.0,2014.

- [9] Shoaib Ahmed Khan, "Digital Design of Signal Processing Systems: A Practical Approach".