# An Efficient Implementation of the LMS Adaptive Algorithm

## Sampath Kumar Dara<sup>1</sup>, Kaparthy Uday<sup>2</sup>

<sup>1</sup>Associate Professor, Vaageswari College of Engineering ,Karimnagar,T.S, India

<sup>2</sup>Assistant Professor, Department of ECE, CVR College of Engineering, Ibrahimpatnam, Hyderabad, T.S, India

Abstract: This paper displays the minimum mean-square (LMS) versatile channel for determining its Architectures for rapid and low multifaceted nature usage. It is demonstrated that the immediate structure LMS versatile channel has about the same basic way as its transpose-structure partner, however gives much speedier joining and lower register multifaceted nature. From the basic way assessment, it is further demonstrated that no pipelining is required for executing an immediate structure LMS versatile channel for most reasonable cases, and can be acknowledged with a little adjustment delay in situations where a high testing rate is required. In view of these discoveries, this paper proposes three structures of the LMS versatile channel: (i) Design 1 having no adjustment delays, (ii)Design 2 with one and only adjustment delay, and(iii) Design 3 with two adjustment delays. Design1 includes the base zone and the base vitality per test (EPS). We present here the advancement of configuration to diminish the quantity of pipeline deferrals alongside the zone, examining period, and vitality utilization. The proposed outline is observed to be more effective regarding the force delay item (PDP) and vitality delay item (EDP) contrasted with the current structures.

Keywords: Adaptive Filters, Critical-Path Optimization, Least Mean Square Algorithms, LMS Adaptive Filter

## 1. Introduction

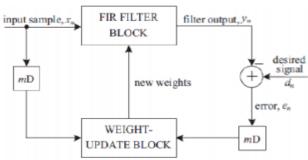

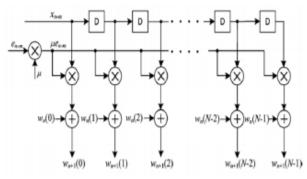

The slightest mean square (LMS) versatile channel is the most well known and generally utilized versatile channel, on account of its effortlessness and its attractive joining execution. The immediate structure LMS versatile channel includes a long basic way because of its internal item calculation to get the yield from channel such that the basic way is required to be diminished by pipelined usage when it surpasses to craved specimen period. In any case, the routine LMS calculation does not bolster for pipelined execution due to its recursive conduct, so they are altered to a structure called the postponed LMS (DLMS) calculation, which permits pipelined usage of the channel. A considerable measure of work has been done to execute the DLMS calculation in systolic designs to expand the recurrence be that as it may, they include an adjustment delay For channel length N, this is entirely high for substantial request channels. We proposed a 2-bit augmentation cell, and with an effective snake tree for pipelined internal item calculation to minimize the basic way and silicon region without expanding the quantity of adjustment deferrals. The current work on the DLMS versatile channel does not talk about with the altered point usage issues, for example, the area of radix point, decision of word length, and quantization at different phases of calculation. Accordingly, settled point usage in the proposed plan lessen the quantity of pipeline deferrals alongside the range, testing period, and vitality utilization. The proposed configuration is observed to be more proficient as far as the force delay item (PDP) and vitality delay item (EDP) contrasted with the current structures. The piece chart of the DLMS versatile channel is appeared in Fig.1, demonstrates the adjustment deferral of m cycles adds up to the postponement presented by the entire of versatile channel structure comprising of limited drive reaction (FIR) separating and the weight-upgrade process. The adjustment postponement of routine LMS can be decayed into two sections: initial segment is the deferral

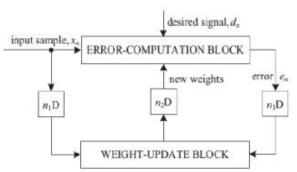

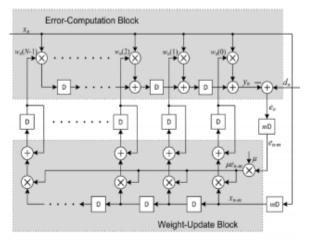

presented by the pipeline stages in FIR sifting, and the other part is because of the deferral required in pipelining the weight overhaul process. Taking into account such a deterioration of deferral, the DLMS versatile channel can be actualized by a structure appeared in Fig.2. The changed DLMS calculation decouples the blunder calculation piece and the weight-redesign square and permits performing ideal pipelining by food forward slice set retiming to minimize the quantity of pipeline stages and change delay. The conformity delay gets diminished in DLMS in view of its pipelined structure, however in customary structure of DLMS, the systolic designs are utilized such that there exist a high adjustment delay. This engineering bolsters high examining recurrence, however includes huge pipeline profundity, which has two unfavorable impacts. To begin with, the register unpredictability, and thus the force dispersal, increments. Furthermore, the adjustment delay increments and merging execution debases.

Notwithstanding, in the accompanying exchange, we build up that such forceful pipelining is regularly uncalled for, since the supposition that the number juggling operations begin simply after era of their complete info operand words is not substantial for the execution of composite capacities in committed equipment. Such a presumption could be legitimate when multipliers and adders are utilized as discrete segments, which is not the situation in ASIC and FPGA execution nowadays. Then again, we can accept that number-crunching operation Besides, we have a demonstrated that no pipelining is required for executing the LMS calculation for most useful cases, and could be acknowledged with little adaption deferral of maybe a couple tests in cases like radar applications where high inspecting rate is required. The most noteworthy testing rate, which could be as high as 30.72 Msps, upheld by the speediest remote correspondence standard (long haul development)LTE-Advanced.

Figure 1: Structure of Conventional LMS Adaptive Filter

Figure 2: Structure of Delayed LMS Adaptive Filter.

Additionally, calculation of the channel yield and weight redesign could be multiplexed to share equipment assets in the versatile channel structure to diminish the range utilization. Further exertion has been made by Me her and to diminish the quantity of adjustment postponements and also the basic way by a streamlined execution of the inward item utilizing a bound together pipelined convey spare chain in the forward way have proposed a 2-bit augmentation cell, and utilized that with an effective snake tree for the usage of pipelined internal item calculation to minimize the basic way and silicon territory without expanding the quantity of adjustment deferrals. Be that as it may, in these works, the basic way examination and fundamental outline contemplations are not considered. Because of that, the outlines of still expend higher region, which could be significantly lessened. Remembering the above perceptions, we display a precise basic way investigation of the LMS versatile channel, and in light of that, we infer design for the LMS versatile channel with negligible utilization of pipeline stages, which will bring about lower territory many-sided quality and less power utilization without bargaining the coveted preparing throughput. Whatever is left of the paper is sorted out as takes after. In the following segment, we audit the immediate frame and transpose-structure usage of the DLMS calculation, alongside their merging conduct. Whatever is left of the paper is composed as takes after. In Section II, Least Mean Square Adaptive Filters. Proposed Work is talked about in Section III. The execution of the proposed plans as far as equipment necessity, timings, and force utilization is talked about in Section IV. Conclusions are introduced in Section V.

2. Least Mean Square Adaptive Filters

The Least Mean Square versatile channel is the most prevalent and most broadly utilized versatile channel, in view of its effortlessness as well as in light of its attractive meeting execution. The immediate structure LMS versatile channel includes a long basic way because of an internal item calculation to acquire the channel yield. The basic way is required to be decreased by pipelined execution when it surpasses the wanted example time frame. Since the routine LMS calculation does not bolster pipelined execution due to its recursive conduct, it is altered to a structure called the postponed LMS (DLMS) calculation, which permits pipelined usage of the channel. A great deal of work has been done to actualize the DLMS calculation in systolic designs to expand the most extreme usable recurrence at the same time, they include an adjustment postponement of N cycles for channel length N, which is entirely high for vast request channels. Since the merging execution debases impressively for an extensive adjustment delay, have proposed a changed systolic design to decrease the adjustment delay. A transpose-structure LMS versatile channel is proposed, where the channel yield at any moment relies on upon the postponed forms of weights and the quantity of deferrals in weights shifts from 1 to N. Van and Feng have proposed a systolic design, where they have utilized generally extensive handling components (PEs)for accomplishing a lower adjustment delay with the basic way of one MAC operation. In this outline channel coefficients are stacked in bit parallel structure with no expansion in the quantity of information pins, along these lines encouraging and accelerating run-time adjustment to the application environment. This sort of configuration strategies can be connected for the outline of utilization particular and implanted parallel models.

#### A. Issues Identified

- In reality, to make sure that the coefficients don't wander, an utmost of 0.6µmax is picked.

- The versatile channels have turned out to be helpful in these situations of various info/yield, variation time practices, and long and complex exchange works successfully, however on a very basic level despite everything they need to develop.

- LDB is the predefined rationale profundity bound that restricts the greatest rationale profundity of the MCM.

- The Total Power dissemination is high.

- Existing does not decrease the equipment many-sided quality without observable debasement.

# 3. Proposed Work

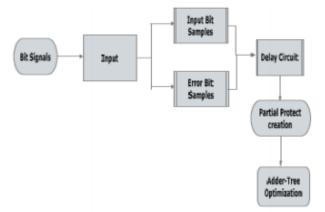

The existing system consists more add and multiply operators and consumes more power, accuracy to be low and the path delay also increased. The system performance is too low. The Proposed system used to the FIR digital filter architecture for the digital image processing application and to modify the area for FIR filter architecture as shown in Fig.3.

Figure 3: Block Diagram of the proposed method.

- Pre-handling

- Partial secure era

- Shift-include design

- Delay-viper unit

Pre-Processing: The information bit to apply the deferral circuit. The movement procedure to include the pre-handling segment in the meantime the error bit to apply the deferral unit area the error bit to apply the co-effective square and go the following DA-based PPG piece. At that point the info is successively apply to the adjusted halfway ensure era circuit. Incomplete Protect Generation: The changed halfway ensure era to be apply the info signal and the error signal. The DA based convey spare snake engineering used to the PPG expansion process. The changed PPG circuit used to alter settled point LMS versatile calculation. The proposed settled point LMS calculation to apply the altered PPG design it is utilized to decrease the example mean PPG circuit.

Shift-Add Architecture: The adjusted PPG circuit yield to be given to the multiplier design. The lessened duplicate administrator utilizing shift-include tree technique. This technique used to enhance the multiplier entryway check. So diminish the force utilization level. To perform the whole operations overlooking the last item, the routine design for movement and include multipliers require numerous exchanging exercises. The PPG circuit yield to be given to the multiplier engineering. The duplicate administrator utilizing shift include tree strategy. This strategy used to enhance the multiplier door number. So lessen the force utilization level.

Delay-Adder Unit: The decreased postponement snake unit to be apply the contribution for movement include The postponement unit to apply the engineering. successively in this operation so the last yield to be delivered and we utilizing the altered point LMS versatile calculation to diminish the deferral circuit and to enhance the proposed framework This productivity of channel engineering to decrease the force utilization level and to enhance the convey choice handling DA-based channel design. The slightest mean-square (LMS) is an inquiry calculation in which a disentanglement of the inclination vector calculation is made conceivable by properly altering the goal capacity. The LMS calculation, and additionally others identified with it, is broadly utilized as a part of different utilizations of versatile sifting because of its computational straightforwardness. The union attributes of the LMS calculation are analyzed so as to set up a reach for the union element that will promise solidness. The joining velocity of the LMS is appeared to be reliant on the Eigen esteem spread of the info signal relationship lattice. In this section, a few properties of the LMS calculation are talked about incorporating the mis alteration in stationary and non stationary situations and following execution the examination results are confirmed by a substantial number of recreation cases supplements this breaking down the limited word length impacts in LMS calculation.IV.

#### 4. Complexity Considerations

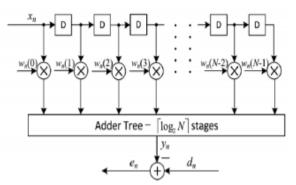

The equipment and time complexities of the proposed and existing outlines are recorded in Table I. A transpose-shape fine grained retimed DLMS (TF-RDLMS), a tree directframe fine grained retimed DLMS (TDF-RDLMS) [11], the best of systolic structures [6], and our latest direct-shape structure [10] are contrasted and the proposed structures. The proposed plan with 0, 1, and 2 adjustment postponements are alluded to as proposed Design 1, Design 2, and Design 3, in Table I. The immediate structure LMS and transpose-structure LMS calculation taking into account the structure of Figs. 4, 5, and 6 with no adjustment delays, e.g., m =0, and the DLMS structure proposed in [4] are likewise recorded in this table for reference. It is found that proposed Design 1 has the longest basic way, yet includes just a large portion of the quantity of multipliers of different outlines with the exception of [10], and does not require any adjustment delay. Proposed Design 2and Design 3 have less adaption delay contrasted with existing outlines, with the same number of adders and multipliers, and include less defer registers.

Figure 4: Error-computation block of Fig. 2

We have coded all the proposed designs in VHDL and synthesized them using the Synopsys Design Compiler with the TSMC 90-nm CMOS library for different filter orders. The structures of [11], [6], and [10] were also similarly coded, and blended utilizing the same instrument. The wordlength of info tests and weights are been 12, and inner information are not truncated before the calculation of channel yield yn to minimize quantization commotion. At that point, en is truncated to 12 bits, while the progression size  $\mu$  is been (1/2k )to understand its duplication with no extra hardware.

### Volume 5 Issue 6, June 2016 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY

Figure 5: Weight-update block of Fig. 2.

Figure 6: Structure of transpose-structure DLMS versatile channel.

The extra adjustment delay m could be at most 2 if no more postpones are fused inside the increase unit or between the multipliers and adders. On the off chance that one deferral could be put after the calculation of y n and another after the calculation of en, then m=2.

# 5. Conclusion

In this anticipate the fundamental goal is to decrease an area- delay-power effective low adjustment delay engineering for settled point usage of LMS versatile channel. We utilized a novel PPG for effective usage of general increases and inward item calculation by regular sub expression sharing. Furthermore, we have proposed a proficient expansion plan for internal item calculation to diminish the adjustment defer fundamentally with a specific end goal to accomplish speedier union execution and to decrease the basic way to bolster high info testing rates. Beside this, we proposed a procedure for enhanced adjusted pipelining over the tedious squares of the structure to decrease the adjustment postpone and control utilization, too. The proposed structure included altogether less adjustment postpone and gave critical sparing of ADP and EDP contrasted with the current structures. The most noteworthy examining rate that could be upheld by the ASIC usage of the proposed outline when the versatile channel is required to be worked at a lower testing rate, one can utilize the proposed plan with a clock slower than the greatest usable recurrence and a lower working voltage to lessen the force utilization further

# References

- [1] Pramod Kumar Meher, Senior Member, I.EEE, and Sang Yoon Park, Member, IEEE, —Critical-Path Analysis and LowComplexityImplementation of the LMS Adaptive Algorithml, IEEE Transactions on Circuits and Systems—I: Regular Papers, Vol. 61, No. 3, March 2014.

- [2] B. Widrow and S. D. Stearns, Adaptive Signal Processing. EnglewoodCliffs, NJ, USA: Prentice-Hall, 1985.

- [3] S. Haykin and B. Widrow, Least-Mean-Square Adaptive Filters.Hoboken, NJ, USA: Wiley-Interscience, 2003.

- [4] G. Long, F. Ling, and J. G. Proakis, —The LMS algorithmwith delayedcoefficient adaptation, IEEE Trans. Acoust., Speech, Signal Process., vol. 37, no. 9, pp. 1397–1405, Sep. 1989.

- [5] M. D.Meyer and D. P. Agrawal, —Amodular pipelined implementation f a delayed LMS transversal adaptive filter, l in Proc. IEEE Int. Symp.Circuits Syst., May 1990, pp. 1943–1946.

- [6] L. D. Van and W. S. Feng, —An efficient systolic architecture for theDLMS adaptive filter and its applications, IEEE Trans. Circuits Syst.II, Analog Digit. Signal Process, vol. 48, no. 4, pp. 359–366, Apr.2001.

- [7] L.-K.Ting,R.Woods, andC. F. N. Cowan, —Virtex FPGAimplementationof a pipelined adaptive LMS predictor for electronic support measuresreceivers, IEEE Trans. Very Large Scale Integr. (VLSI) Syst.,vol. 13, no. 1, pp. 86–99, Jan. 2005.

- [8] E. Mahfuz, C. Wang, and M. O. Ahmad, —A highthroughput DLMSadaptive algorithm, in Proc. IEEE Int. Symp. Circuits Syst., May 2005, pp. 3753– 3756.

- [9] P. K.Meher and S. Y. Park, —Lowadaptation-delay LMS adaptive filterPart-II: An optimized architecture, in Proc. IEEE Int. Midwest Symp.Circuits Syst., Aug. 2011.

- [10] P. K. Meher and S. Y. Park, —Area-delay-power efficient fixed-pointLMS adaptive filter with low adaptation-delay, Trans. Very LargeScale Integr. (VLSI) Signal Process. [Online]. Available: http://ieeexplore.ieee.org.

- [11] Y. Yi, R. Woods, L.-K. Ting, and C. F. N. Cowan, —High speedFPGA-based implementation of delayed-LMS filters, Trans. VeryLarge Scale Integr. (VLSI) Signal Process, vol. 39, no. 1–2, pp.113–131, Jan. 2005.

- [12] S. Y. Park and P. K. Meher, —Low-power, highthroughput, and lowareaadaptive FIR filter based on distributed arithmetic, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 60, no. 6, pp. 346–350, Jun. 2013.