# Enhancement of Solar Cell Efficiency in Solar Manufacturing Plant

## N Sindhu<sup>1</sup>, P Mabuhussain<sup>2</sup>

<sup>1,2</sup>Institute of Aeronautical Engineering, Department of Electrical and Electronics Engineering Dundigal Village, Hyderabad – 500043, Telangana, India

Abstract: At present, the typical efficiency of PV Modules is in the range of 13 to 14% at module level. With continuous technological innovations, demand of high efficiency (>15%) PV Modules is increasing. Improving the efficiency of PV modules in the manufacturing process comprises of using high efficiency solar cells, increasing the number of bus bars, using anti-reflection coated glass etc. The efficiency of solar PV cell has increased by using Double Layer Anti Reflective coating from 15% to 17.4%. The efforts are made to increase the solar cell efficiency by changing different parameters like temperature, flow rate of  $N_2$  and  $O_2$  in diffusion process and the efficiency is improved to 18.19% in BHEL EDN Bangalore solar manufacturing plant.

Keywords: Solar cell, sheet resistance, anti reflection coating, diffusion process, cell efficiency etc.

### 1. Introduction

In 1839 Alexander Edmond Becquerel discovered the photovoltaic effect which explains how electricity can be generated from sunlight. He claimed that "shining light on an electrode submerged in a conductive solution would create an electric current." However, even after much research and development subsequent to the discovery, photovoltaic power continued to be very inefficient and solar cells were used mainly for the purposes of measuring light. Over 100 years later, in 1941, Russell Ohl invented the solar cell, shortly after the invention of the transistor

At present crystalline silicon solar cells are more established and mostly used to generate electricity rather than using thin films crystalline silicon solar cells, amorphous silicon solar cells, because they attain less efficiency. Though thin film silicon solar cells are available at lesser cost/watt, the startup facilities cost & complexity of manufacturing processes very high and also thin film field performance data for power plants is not available for 25 years as that of crystalline technology.

So, Improvement in efficiency of crystalline silicon solar cells is very much relevant today from the point of view of cost reduction. Some of the very promising approaches for efficiency improvement for conventional silicon solar cells manufactured with screen printing technology are modification in the existing screen printing, selective emitter, back surface passivation, multilayer Anti-reflection coating and other technologies etc. These technologies boost the efficiency of a solar cell by 1-2%.

There are a number of means available to increase solar panel output and efficiency — some of which may be utilized by the serious experimenter. Junction formation is the process in which the required impurities are deposited / penetrated in the wafer surface in such a way that the minority carriers in the starting material are not degraded. This process is also called "Diffusion of Impurities" the impurity profile has to be tailored for highest conversion efficiency. A thin film of silicon nitride (anti-reflection coating) is deposited on the wafer to lower the reflection of light further and to passivity the solar cell against harmful environment such as humidity, ionizing radiation and reactive module lamination materials. Anti-reflection coating enhances the solar cell conversion efficiency by almost 1 %. In this paper the efforts are made further to improve the solar efficiency in solar cell manufacturing plant by changing the different parameters such as temperature, flow rate of N<sub>2</sub> and O<sub>2</sub> in the diffusion process.

# 2. Manufacturing Process of Solar Cells

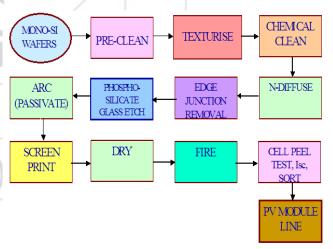

Figure 1: Manufacturing Process of Solar Cells

#### **Starting Wafer**

Crystalline silicon p-type boron diffused, 200 +/- 20 microns thick, 156\*156 mm Pseudo square, imported from Japan.

#### Saw damage removal and Texturisation

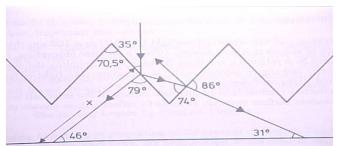

The silicon wafers are chemically etched in concentrated alkali solution to remove saw damages followed by a dilute alkali text rising step to form pyramid-like structures on the wafer. Process parameters such as alkali concentration, solution temperature and process time are optimized to get well-defined normal random pyramids which enhance the surface area of the wafer for greater light absorption and at the same time, facilitate total internal reflection of light.

Figure 2: Reflection angle on the textured pyramidal structure of silicon wafers

#### **Pre-Diffusion cleaning**

This process is done immediately after the Texturisation, so that Alkali is neutralized with the Acid. HF and HCL in proper proportion is used. HF removes oxide layer and cleans the surface, this is important before Diffusion process.

### P-N Junction formation by thermal Diffusion

Junction formation is the process in which the required impurities are deposited / penetrated in the wafer surface in such a way that the minority carriers in the starting material are not degraded. This process is also called "Diffusion of Impurities" the impurity profile has to be tailored for highest conversion efficiency. The required n-type layer is deposited over the p-type silicon wafer to get a simple P-N junction. The n-type dopant generally added will be phosphorous in the form of liquid. Several techniques are used for the formation of the junction.

| Table 1: Recipe | for diffusion | of sheet Resistar | ice of 55 $\Omega/m^2$ |

|-----------------|---------------|-------------------|------------------------|

|                 |               |                   |                        |

| Stong     | Time  | Load | Center | Source | $N_2$  | $O_2$  | POCl <sub>3</sub> |

|-----------|-------|------|--------|--------|--------|--------|-------------------|

| Steps     | (min) | (°C) | (° C)  | (° C)  | (SLPM) | (SLPM) | (SCCM)            |

| Idle      | 0     | 750  | 750    | 750    | 15     | 0      | 0                 |

| Boat in   | 6     | 700  | 700    | 700    | 15     | 0      | 0                 |

| Stabilize | 7     | 700  | 700    | 700    | 30     | 0      | 0                 |

| Ramp up   | 20.01 | 850  | 810    | 820    | 27     | 0      | 0                 |

| Doping    | 30    | 850  | 810    | 820    | 15     | 0.7    | 1300              |

| Drive in  | 30    | 860  | 820    | 830    | 15     | 0.7    | 0                 |

| Ramp      | 15    | 750  | 750    | 750    | 27     | n      | 0                 |

| down      | 15    | 750  | 750    | 750    | 4      | · •    |                   |

| Boat out  | 6     | 750  | 750    | 750    | 15     | 0      | 0                 |

| Process   | 0.02  | 750  | 750    | 750    | 15     | 0      | 0                 |

A p-n junction is then formed on the textured silicon wafer through a high-temperature, solid- state diffusion process in a quartz furnace. In this process, phosphorous oxy-chloride (POCl3) liquid dopant is deposited on the wafers and is driven in when a thin n-type layer is formed.

Phosphorous oxy-chloride (POCl3) is a n-type material which is in the liquid form bubbled through the nitrogen gas and deposited on to the wafers in vaporized condition in a Diffusion Furnace. Diffusion in the gaseous phases at around 850 to 950°C, this is the most popularly used method. The diffusion furnace which is having temperature controlled heating system having high degree of accuracy with the dopant control system is used. Silicon wafers are loaded onto quartz Boat and pushed into hot zone in the closed gaseous atmosphere for the duration until the required surface

concentration and depth is achieved. This most priority is given for cleanliness to ensure that the wafers are not contaminated during the entire process. The only disadvantage of this method is that dopant will be deposited on both side and as well as at the periphery of the wafers, where as doping is needed only on one surface, the unwanted areas will be removed in subsequent stage.

Entire process time = 2 Hrs.

Through puts = 200\*2\*3 = 1200 Nos. in 3 tubes per run. Diffusion furnace is from MRL Industries, USA.

Figure 3: Solar cells placed in Diffusion Furnace

## Sheet Resistance $(\Omega/m^2)$

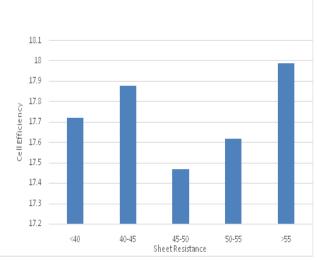

Silicon wafer is placed in sheet resistance equipment, sheet resistance equipment shows wafer as n-type then wafer is pass (i.e. changed p-type to n-type wafer in thermal diffusion). If sheet resistance is more power generated is more, but in BHEL Sheet Resistance is restricted to 45-60  $\Omega$ /sq.

### **Edge Isolation & PSG Removal**

The junction formed in diffusion process has to be isolated with the edge of the wafer. This can be done either by chemical (wet) process or through Plasma Etching (Dry) process.

### Silicon Nitride Anti-Reflection Coating (ARC)

Silane (SiH<sub>4</sub>) and Ammonia (NH<sub>4</sub>) gas in proper proportion is let inside the Tube which is at 450° c. Graphite boat loaded with 144 wafers of 156 mm size is loaded into the tube where in Silane and Ammonia reacts with silicon in the presence of RF power fed to the + ve and - ve probes of the boat which gives a Silicon Nitride (SiN) coating on the wafer surface. The Refractive index of this film is 2.05 and coating thickness is around 80 nano meters, which absorbs the maximum light spectrum into material. Anti-reflection coating enhances the solar cell conversion efficiency by almost 1 %. After completing the ARC coating solar cell is placed in the reflection measuring equipment and measuring the reflection and absorption of sun radiation percentages in digital display. After ARC coating Absorption of solar cell percentage is increased from 70% to 90% and Reflection of solar cell percentage is decreased from 30% to 10%.

# 3. Testing at BHEL EDN Bangalore

Heavy Electricals Bharat Limited has established semiconductor manufacturing facilities at its Electronics Division and it is established in 1983. Bangalore where it manufactures 125-mm / 156-mm pseudo square mono crystalline silicon solar cells with power output of 2.5 / 3.9 watts and solar cell conversion efficiency of 16.5 %. Photovoltaic modules are constructed with 36/60/72 (for 12/20/24 V) solar cells which are interconnected in series configuration and yield a power output of 80 to 270 watt. PV modules of 170-watt / 220 -watt rating are interconnected in series (PV array) - parallel configuration in the case of a grid interactive power plant to obtain the required voltage and power output for the power plant.

#### Diffusion

To form emitter the doping is same beneath the metal contacts and between the fingers. To maintain low resistance (contact) high surface concentration of phosphorus is required below the screen printing contact. High surface concentration of phosphorus produces a "dead layer" that reduces the cell blue response. Newer cell designs can contact shallower emitters, thus improving cell blue response. Selective emitters with higher doping below the metal contacts have also been proposed, but none have yet been introduced into commercial production.

Table 2: Current set points

| Process | Time  | Temper | rature (°C         | $N_2$ | <b>O</b> <sub>2</sub> |       |  |

|---------|-------|--------|--------------------|-------|-----------------------|-------|--|

| 1100035 | (min) | Load   | Load Center Source |       |                       | (lpm) |  |

| Doping  | 30    | 850    | 810                | 820   | 1500                  | 70    |  |

#### Segregation of cells based on sheet resistance

The solar cells are tested under Sun Simulator. There were ten grades based on the efficiency of solar cell. The highest efficiency i.e, >18% is considered as M grade and the remaining two important grades are as follows:

Table 3: Classification of Cell Efficiency with grade

| M grade | >18%     | Dlin |

|---------|----------|------|

| L grade | 17.5-18% | ''ne |

| K grade | 17-17.5% |      |

| Table 4: | Segregation | of cells |

|----------|-------------|----------|

|----------|-------------|----------|

| Cell Efficiency | M   | L   | K   | Total |

|-----------------|-----|-----|-----|-------|

| 17.40           | 0   | 2   | 52  | 99    |

| 17.51           | 2   | 20  | 2   | 30    |

| 17.35           | 8   | 7   | 1   | 17    |

| 17.48           | 546 | 793 | 573 | 3409  |

# 4. Experiment

The above technique was being used in BHEL EDN Bangalore and now the proposed technique is by changing current set points and increasing the number of bus bars. A detailed experiment was done and is conveyed as below.

|      | Tal                              | ble 5: | Base | readin | gs fo           | r Dopi | ng Pro   | ocess |       |  |  |

|------|----------------------------------|--------|------|--------|-----------------|--------|----------|-------|-------|--|--|

| T:   | Temperature                      |        | N    | 0      | 96 <sup>n</sup> | She    | et Resis | tance |       |  |  |

| Time | L                                | С      | S    | $IN_2$ | $O_2$           |        | L        | С     | S     |  |  |

| 30   | 850                              | 810    | 820  | 1500   | 70              | 17.2   | 49.9     | 54.66 | 53.07 |  |  |

|      | L = Load, C = Center, S = Source |        |      |        |                 |        |          |       |       |  |  |

| Table 6: E | xperiment Schemes |

|------------|-------------------|

|------------|-------------------|

|                           | Parameters        |                    | Recipe | % η of Cell |       |

|---------------------------|-------------------|--------------------|--------|-------------|-------|

| Temp                      | $N_2$             | O <sub>2</sub>     | ID     | Average     | STDEV |

| Current                   | Current           | Current - 2<br>lpm | 1      | 18.07       | 0.39  |

| Current -5 Current +3 lpm |                   | Current - 2<br>lpm | 2      | 18.75       | 0.14  |

| Current                   | Current +3<br>lpm | Current            | 3      | 18.64       | 0.19  |

| Current -5<br>deg         | Current           | Current            | 4      | 18.18       | 0.29  |

In the above table, Design of Experimental schemes is shown. Recipes were made by changing different parameters such as Temperature & Mass flow rate of Nitrogen N2 (lpm), OxygenO2 (lpm) in diffusion process.

The changes were made compared to the regular recipe, it shows that there is no improvement in recipe 1,3and 4 efficiency. But In Recipe 2,changes in all parameter were made such as temperature decrease by 5 degree, flow rate of Nitrogen (N2) increased by 3 liters per minutes and Oxygen (O2) decreased by 2 liters per minutes, calculated efficiency for recipe 2 is 18.75% comparing to all recipes, it is found to be more effective.

Table7: Variation in Sheet Resistance

|   | Table 7: Variation in Sheet Resistance |         |             |        |                        |                     |  |  |  |  |

|---|----------------------------------------|---------|-------------|--------|------------------------|---------------------|--|--|--|--|

| 1 | Recipe                                 | Load    | Center      | Source | Avg R <sub>sheet</sub> | DOE                 |  |  |  |  |

| 1 | 1                                      | 1 46.14 |             | 74.64  | 61.58                  | Low O2              |  |  |  |  |

| - | 2                                      | 52.8    | 62.98       | 64.82  | 60.20                  | All Changed         |  |  |  |  |

|   | 3                                      | 53.84   | 4 53.6 48.4 |        | 51.95                  | High N <sub>2</sub> |  |  |  |  |

|   | 4                                      | 55.72   | 62.54       | 60.48  | 59.48                  | Low Temp.           |  |  |  |  |

|   |                                        |         |             |        |                        |                     |  |  |  |  |

Figure 4: Variation of sheet resistance v/s cell efficiency

Recipe 2 is formed to be more effective observed wide variation in sheet resistance across the tube so need to find out the optimum sheet resistance for maximum efficiency.

#### • Yield improvement at sheet resistance 55-60 ohms:

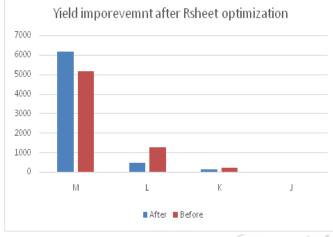

Figure 5: yield improvement

## 5. Results

Table 8: Numbers of cells before and after yield improvement

| inipio (eniterit |      |      |     |    |    |   |    |    |    |    |

|------------------|------|------|-----|----|----|---|----|----|----|----|

| Day              | М    | L    | Κ   | J  | Ι  | H | G  | F  | Е  | ER |

| Before           | 5166 | 1259 | 237 | 21 | 14 | 9 | 11 | 25 | 7  | 20 |

| After            | 6167 | 478  | 138 | 19 | 11 | 3 | 9  | 9  | 13 | 20 |

|                  |      |      |     |    |    |   |    |    |    |    |

Graph shows improvement in yield of the highest grade cells after implementing the optimization.

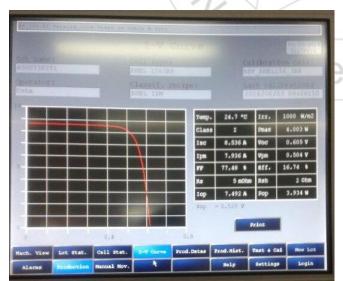

Before conducting the experiment i.e. changes are not done in diffusion process the result as shown in below. The 72 cells PV module wattage 258.276 watts and 60 cells PV module wattage 215.230 watts

Figure 6: Output in Sun Simulator before Changes are done in Diffusion Process

• Cell Efficiency=16.74%

• Module Wattage for 60 cells is Module Wattage = Iop\* Vop \* 60 \* 0.95 = 7.492 \* 0.504 \* 60 \* 0.95 Module Wattage = 215.230 watts

• Module Wattage for 72 cells is Module Wattage = Iop\* Vop \* 72 \* 0.95 = 7.492 \* 0.504 \* 72 \* 0.95

Module Wattage = 258.276 watts

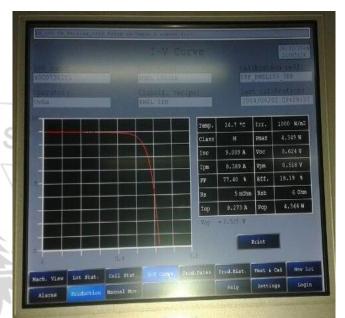

After conducting the experiment, i.e. changes are done in diffusion process the result as shown in below. The 72 cells PV module wattage 328.553watts and 60 cells PV module wattage 273.794 watts.

Figure 7: Output in Sun Simulator after Changes are done in Diffusion Process

Cell efficiency=18.19%• Module Wattage for 60 cells is Module Wattage = Iop\* Vop \* 60 \* 0.95 = 9.273 \* 0.518 \* 60 \* 0.95 Module Wattage = 273.794 watts.

• Module Wattage for 72 cells is Module Wattage = Iop\* Vop \* 72 \* 0.95 = 9.273\* 0.518 \* 72 \* 0.95 Module Wattage = 328.553watts

# 6. Conclusion

The efficiency of PV Modules is in the range of 13 to 14% at module level. Improving the efficiency of PV modules in the manufacturing process comprises of using high efficiency solar cells, increasing the number of bus bars, using anti-reflection coated glass etc. The efficiency of solar PV cell has increased by using Double Layer Anti Reflective coating from 15% to 17.4%. In this paper the efforts are made to increase the solar cell efficiency by changing different parameters like temperature, flow rate of  $N_2$  and  $O_2$  in diffusion process. After changing the parameters of temperature, flow rate of  $N_2$  and  $O_2$  the cell efficiency is increased up to 18.75%, and if 60 and 72 solar cells of these

sr.ner

2319

types are arranged as a PV Module, then the wattage is increased up to 273.794 watts and 328.553 watts respectively.

## References

- Ghanim A. Al-Jumaily, F.J. Gagliardi, P. McColl and Lawrence Mizerka, in 'Ion-assisted deposition of graded index silicon oxynitride coatings'; Proceedings SPIE 1441, 1991, pp. 360-364; Paul G. Snyder, Yi-Ming Xiong and John A. Woollam, Ghanim A. Al-Jumaily and F.J. Gagliardi, in 'Graded refractive index silicon oxynitride thin film characterized by spectroscopic ellipsometry'; J. Vac. Sci. Technol. A 10(4), 1992, p. 1462-1466.

- [2] M.I. Smokler, D.H. Otth and R.C Ross Jr., "The Block Approach to Photovoltaic Module Development", Proceedings of the 18th IEEE Photovoltaic Specialist Conference, 1985, p. 1150.

- [3] Multi-layer Antireflection Coatings; www.mellesgriot.com

- [4] R. Swanson, Conference Record of the 31st IEEE Photovoltaic Specialists Conference, Jan 3-5, 2005, p. 889, in 'Approaching the 29% limit efficiency of silicon solar cells'.

- [5] J. P. Pinto, R. Pregitzer, L. F. C. Monteiro, and J. L. Afonso, "renewable energy interface," presented at the Conf. IEEE Rnewable Energy & Power Quality, Seville,Spain, 2007

# **Author Profile**

N Sindhu is currently working as an Assistant Professor in Institute of Aeronautical Engineering, Hyderabad. She received M. Tech degree with specialization in Energy Systems in 2014 from Jawaharlal Nehru Technological University of her B. Tach degree from correct University

Anantapur and her B. Tech degree from same University with specialization in Electrical and Electronics Engineering in 2012. Her areas of interest are Solar Energy, Power systems and Control Systems.

**P Mabuhussain** is currently working as an Assistant Professor in Institute of Aeronautical Engineering, Hyderabad. He received M. Tech degree from Jawaharlal Nehru Technological University Anantapur, with specialization in Energy Systems in 2014, and B.

Tech degree from Sri Venkateswara University, Tirupati with specialization in Electrical and Electronics Engineering in 2012. His areas of interest are Solar Energy, Electrical Machines and Control Systems.