International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

# Low Power Self-Timed TCAM Based on Overlapped Search Mechanism with IP Filter Implementation

Jerrin Paul M<sup>1</sup>, Hazel Elsa John<sup>2</sup>

<sup>1</sup>M.Tech Student, Department of Electronics and Communication Engineering, SCMS School of Engineering and Technology, Karukuuty, Cochin, Kerala, India

<sup>2</sup>Assistant Professor, Department of Electronics and Communication Engineering SCMS School of Engineering and Technology, Karukuuty, Cochin, Kerala, India

**Abstract:** A self timed TCAM based on the overlapped search mechanism was introduced. This paper introduces a performance evaluation of the power, delay, area of the self timed CAM and TCAM. To lower the power dissipation the word circuit is often divided into two sections that are sequentially searched or even pipelined. This paper presents realizes the high performance and low power TCAM for IP filter implementation. In this 128-64 bit TCAM is implemented and evaluated by XILINX ISE 8.1i. The TCAM achieves reduced power and delay.

Keywords: Content addressable memories, ternary content addressable memories

#### 1. Introduction

Content addressable memories compares input search data against a table of stored data and returns the address of the matching word.CAM can be used in a wide variety of application requiring high search speed. TCAM is a type of the content addressable memory. TCAM can accept 0,1,x. One of the most important advantage of the TCAM is that it can accept the don't care values. CAMs and, specifically, ternary CAMs (TCAMs) are used extensively in networking. CAMs provide read and write, such as a normal memory, but additionally support search which will find the index of any matching data in the entire memory. A TCAM extends this functionality to include wildcard bits that will match both one and zero. These wildcards can be used on both the access operations of the memory (indicating some bits of the search are -don't cares") or can be stored with the data itself (indicating some bits of the data should not be used for determining a match). The fully parallel search provided by TCAM eases the implementation of many complex operations such as routing table lookup. The term -ternary" refers to the memory's ability to store and query data using three different inputs: 0, 1 and X. The -X" input, which is often referred to as a -don't care" or -wildcard" state, enables TCAM to perform broader searches based on pattern matching, as opposed to binary CAM, which performs exactmatch searches using only 0s and 1s[1].

This paper presents a reordered overlapped search mechanism for providing high speed and low power. In this mechanism the word circuit is often divided into two segments of different segments that sequentially operate. In this mechanism the smaller segment of the input word matches with the stored word. If the stored word is found then the next search for the large segments is initiated. If the smaller segment does not matches with the stored word then word goes to the unused block. This search mechanism can provide shorter delay and low power. This mechanism can be implemented for the CAM and TCAM. Since TCAM can accept 0,1,don't care value. So in a single search multiple data can be searched. So TCAM offers high speed, low power compared to CAM.TCAM also offers many applications. In this paper IP filter was implemented using TCAM memory. An Ip filter is a security feature that prohibits unauthorized users from accessing LAN resources. It can also restrict IP traffic over a wide area network (WAN link. This paper implements IP filter using TCAM [1].

#### 2. Overlapped search mechanism

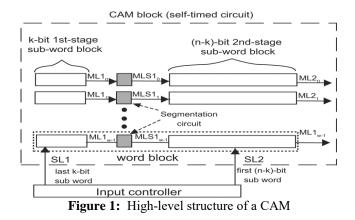

Fig. 1 shows the high-level structure of the CAM based on the WOS scheme. It contains a CAM block that operates using self timed control and an input controller. There are word blocks that store -bit words in the CAM block. The word block is divided into a small -bit sub-word block and its subsequent large (n-k) bit sub-word block using a segmentation circuit. This segmentation method is usually used to reduce the switching activity of the subsequent word blocks.

In the proposed method, input words are searched from the Least Significant Bit (LSB). The 1st-stage segment stores the

#### Volume 4 Issue 9, September 2015 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY

last bits of words and the 2nd-stage segment stores the first (n-k) bit of words. The first k-bit of word is compared with the stored word and if the match is found then it will go to the search of the second stage. Then first k-bit match is not found the search word will go to the unused block and next search was initiated.

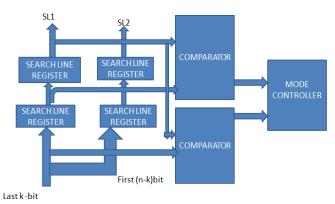

Figure 2: Block diagram of the input controller

Fig 2 shows the block diagram of the input controller. The input controller consist of the register ,comparator ,mode controller. The mode controller operates in two modes fast and slow The last k-bit is compared with the m search word inside the CAM block. If the search word is not found the same then CAM operates in fast mode, so that the CAM operates in high speed.

# 3. Overlapped search mechanism in TCAM

The above proposed method can be used in TCAM.TCAM memory is faster compared to the CAM.TCAM can accept 0,1,don't care values .In a single search multiple data can be searched. So the TCAM is faster compared to CAM.Ternary content addressable memory (TCAM) is an important component for many applications.

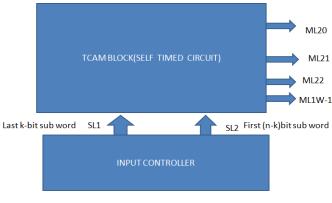

Figure 3: Structure of TCAM

Fig 3 shows the self timed structure of the TCAM.TCAM consist of the input controller, TCAM block. The input controller divides the word bit into k-bit and (n-k)bit word. The structure of the TCAM is same as that of CAM. Since TCAM can search multiple data in a single search. So the TCAM have high speed compared to the CAM.TCAM also have reduced power, area compared to CAM.T he self timed structure of the TCAM consist of the local match and global match. If the k-bit matches with the stored word inside the

TCAM, then it is the local match. If the (n-k)bit matches with the stored word inside the TCAM then it is the global match. The TCAM structure consist of the self-precharge circuit which is the delay element that precharges a matched word circuit after the completion of the current search in the word circuit. TCAM consist of the dummy word circuit to reduce the delay difference between the delay element and the sub word circuit. Hence, once the first segment matches the dummy word circuit also matches and operates as delay elements.

# 4. Simulation Results

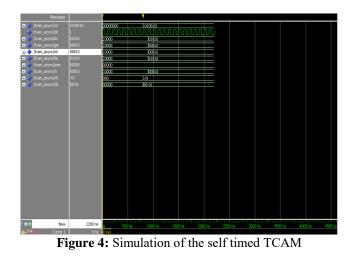

The simulation of the self timed structure of the TCAM,CAM was done in MODELSIM XE 6.3f.The simulation results shows the self timed TCAM,CAM displaying the search data, local match, global match, precharge, match line. The search data is divided into two bits and that can be displayed as sl1,sl2. The local match is the k-bit match. The global match is the (n-k) bit match. The precharge value is the delay element that precharges a match word circuit after the completion of the current search in the word circuit.

Figure 5: Simulation of the self timed CAM

# 5. Performance Evaluation

Table below shows the performance comparison of CAM, TCAM. It includes the comparison of the delay, area, power.

The evaluation of the TCAM, CAM can be done in XILINX ISE 8.1i.

Table 1: Shows the comparison of the delay of the TCAM,

| CAM             |         |  |  |  |  |

|-----------------|---------|--|--|--|--|

| Structure Delay |         |  |  |  |  |

| CAM             | 5.747ns |  |  |  |  |

| TCAM            | 5.140ns |  |  |  |  |

**Table 2**: Shows the comparison of the area of the CAM,TCAM

| Structure | Area |

|-----------|------|

| CAM       | 407  |

| TCAM      | 48   |

From the table 2 shows that the area of the TCAM is greatly reduced than CAM.

Table 3: Shows the power comparison of the CAM, TCAM

| Structure | Power(mW) |

|-----------|-----------|

| CAM       | 56        |

| TCAM      | 34        |

|           |           |

#### 6. IP filter implementation using TCAM

Ternary content addressable memory (TCAM) is an important component for many applications. For TCAM-based networking systems, the rapidly growing size of routing tables brings with it the challenge to design higher search speeds and lower power consumption. Content addressable memory (CAM) is an important component for accelerating data search operation in many applications such as data base access, pattern matching, signal processing , and networking IP address lookup. In some applications such as IP-address lookup, *t*ernary *c*ontent *a*ddressable *m*emory (TCAM) is required to implement the masking function through storing (don't care) in the TCAM cell.

An IP filter is a security feature that prohibits unauthorized users from accessing LAN resources. It can also restrict IP traffic over a wide-area network (WAN) link. With an IP filter, LAN users can be restricted to specific applications on the Internet (such as e-mail). CAM works as a filter to block all access except for packets that have permission. The addresses that have permission are stored in CAM; when an address is sent to memory, CAM reports whether it contains the address. If the address resides within CAM, it has permission for a particular activity.

In the above results shows that TCAM is faster compared to CAM, So this paper implements IP filter using TCAM. The Fig 6 shows the example of an IP filter.In this paper multiple permission IP filter was implemented using the TCAM.

| RAM     |         |                                   |                                             |                                                   |

|---------|---------|-----------------------------------|---------------------------------------------|---------------------------------------------------|

| ADDRESS | DATA    |                                   |                                             |                                                   |

|         | WEB     | EMAIL                             | FTP                                         | TELNET                                            |

| 0       | 1       | 1                                 | 1                                           | 1                                                 |

| 1       | 1       | 1                                 | 0                                           | 0                                                 |

| 2       | 0       | 0                                 | 0                                           | 1                                                 |

|         |         |                                   |                                             |                                                   |

|         | ADDRESS | ADDRESS DATA<br>WEB<br>0 1<br>1 1 | ADDRESS DATA<br>WEB EMAIL<br>0 1 1<br>1 1 1 | ADDRESS DATA<br>WEB EMAIL FTP<br>0 1 1 1<br>1 1 0 |

Figure 6: Multiple permission IP filter

TCAM is faster compared to CAM. So the multiple permission IP filter is implemented using TCAM. The multiple permission IP filter requires RAM memory. RAM operates as a circuit that stores data at a particular address. When retrieving data from RAM, the system supplies the address and then receives the data. With CAM, the system supplies the data instead of the address. To locate stored data, CAM takes one clock cycle to search through all memory locations in parallel and returns the data's address. CAM drives a match flag high if the data is found, or low if the data is not found.

Fig 7 shows the simulation of the multiple permission IP filter implemented using TCAM

Figure 7: Simulation of the multiple permission IP filter

# 7. Conclusion

Content addressable memory (CAM) offers high-speed search function in a single clock cycle. With the invention of Content Addressable Memories (CAM) extensive research has been done to improve performance of throughput, power in past few decades. This paper shows that based on the overlapped search mechanism TCAM (Ternary content addressable memory) offers reduced power, delay, area compared to the content addressable memory. TCAM can accept 0, 1 and don't care values. TCAM can search multiple data in a memory. In a single search multiple data can be found. So the area and power will be reduced. So this paper shows TCAM produce high speed compared to CAM.

CAM can accelerate applications requiring fast searches of databases, lists or patterns and searching the IP addresses. An IP filter is a security feature that prohibits unauthorized users from accessing LAN resources. This paper also implements multiple permission IP filter using TCAM. This paper concludes that TCAM offers high speed, low power compare to CAM.

#### References

- [1] Naoya Onizawa, , Shoun Matsunaga, , Vincent C. Gaudet, Warren J. Gross, and Takahiro Hanyu, "High-Throughput Low-Energy Self-Timed CAMBased on Reordered Overlapped Search Mechanism", IEEE Trans. Very Large Scale Integr. (VLSI) Syst—I: regular papers, vol. 61, no. 3, march 2014.

- [2] H. Jarollahi, V. Gripon, N. Onizawa, and W. Gross, -A low-power content-addressable-memory based on clustered-sparse-networks," in *Proc. 24th IEEE Int. Conf. Application-Specific, Syst., Archit., Processor(ASAP)*, Jun. 2013, pp. 305–308.

- [3] N. Onizawa, S. Matsunaga, V. C. Gaudet, W. J. Gross, and T. Hanyu, –High-throughput CAM based on a synchronous overlapped search scheme," *IEICE Electron. Exp. (ELEX)*, vol. 10, no. 7, p. 20130148, 2013.

- [4] N. Onizawa, S. Matsunaga, V. C. Gaudet, and T. Hanyu, Highthroughput low-energy content-addressable memory based on self-timed overlapped search mechanism," in *Proc. 18th Int. Symp. Asynchronous Circuits Syst.*, May 2012, pp. 41–48.

- [5] N. Onizawa, V. Gaudet, and T. Hanyu, -Low-energy asynchronous interleaver for clockless fully parallel LDPC decoding," *IEEE Trans. CircuitsSyst. I, Reg. Papers*, vol. 58, no. 8, pp. 1933–1943, Aug. 2011.

- [6] A. T. Do, S. S. Chen, Z. H. Kong, and K. S. Yeo, -A lowpower CAM with efficient power and delay trade-off," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, 2011, pp. 2573–2576.

- [7] N. Mohan and M. Sachdev, -Low-leakage storage cells for ternary content addressable memories," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 17, no. 5, pp. 604–612, May 2009.

# **Author Profile**

Jerrin Paul M received the B. Tech degree in Applied Electronics and Instrumentation Engineering from Mahatma Gandhi University, Kerala at Rajagiri School of Engineering and Technology 2013 and now she is pursuing her M. Tech degree in VLSI and

Embedded systems under the same university in SCMS School of Engineering and Technology, Cochin.