## CIC Decimation Filter for Frequency

## Rajesh Kumar Dubey<sup>1</sup>, Kamal Prakash Pandey<sup>2</sup>, Dr. Rakesh Kumar Singh<sup>3</sup>

<sup>1</sup>M.tech 2<sup>nd</sup> year student (VLSI DESIGN), SIET Allahabad, India

<sup>2</sup> Associate Professor, SIET Allahabad, India

<sup>3</sup>Assistant prof. KNIT Sultanpur, India

Abstract: The CIC filters do not require any multiplier circuits and hence are very economical for implementation in hardware and the problems with cascading faced by the accumulate and dump circuit are also overcome with the CIC design. The frequency response of CIC filters has a poor in band frequency response and are mostly used to reduce the decimation factor by large ratio while suitable response sharpening filters work at the reduced rate to get the desired characteristics

Keywords: COMB-BASED FILTER, Cascaded Integrator Comb (CIC) Filter

#### 1. Introduction

Comb filters are developed from the structures based on the moving average (boxcar) filter. The comb based filter has unity-valued coefficients and, therefore, can be implemented without multipliers. This filter class can operate at high frequencies and is suitable for a single-chip VLSI implementation. The main applications are in communication systems such as software radio and satellite communications.

## 1-COMB-BASED FILTER (Cascaded Integrator Comb (CIC) Filter)

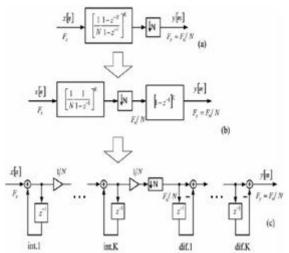

The CIC filter is a combination of digital integrator and digital differentiator stages which perform the operation of digital low pass filtering and decimation. The proposed structure consisted of an integrator block working at the oversampled frequency Fs, a clock divider for rate reduction and a differentiator block working at Fs/k, where k is the decimation ratio. The CIC filters do not require any multiplier circuits and hence are very economical for implementation in hardware and the problems with cascading faced by the accumulate and dump circuit are also overcome with the CIC design. The above design also requires another decimation circuit for decreasing the data rate, which requires additional hardware. Hence it becomes very cumbersome to design the differentiator with many delay elements. The problem with the area can be overcome by implementing a clock divider circuit in between the integrator and differentiator stages as shown in Fig. 2 The clock divider circuit divides the oversampling clock signal by the oversampling ratio K. By dividing the clock frequency by K the number of delay elements used in the differentiator can be reduced to just one. In Fig.2 the integrator operates at the sampling clock frequency, fs while the differentiator operates at down sampled clock frequency of fs/K. By operating the differentiator at lower frequencies, a reduction in the power consumption is achieved.

Figure 1: First order CIC filter with decimation stage

Paper ID: SUB157650

**Figure 2:** Block diagram of a first order CIC filter without external decimation stage. [3]

# 2. Main Performances of A Comb-Based Decimator

The comb-based filters are frequently used as the first decimation stage of the multistage decimators. Because of the simplicity of implementation, the comb filters are suitable for operating at high frequencies. Most importantly, the comb-based filters provide the best solution for the implementation of the first decimation stage in the multistage down-sampling conversion for the oversampled A/D converters.

The aliasing bandwidths around the nulls are narrow, and usually too small to provide sufficient suppression of aliasing in the entire baseband of the signal. And monotonic pass band characteristic produces an inevitable passband droop, which for many applications should be compensated.

The signal band at the decimator input occupies the frequency range [0, Fm]. For the input signal sampling frequency Fx, and for the decimation factor N, the aliasing bands of the bandwidths 2Fm are located around the natural null frequencies Fx/N, 2Fx/N, ..., JFx/N, where J = N/2 for N even, and J = (N)1/2 for N odd.

## **International Journal of Science and Research (IJSR)**

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

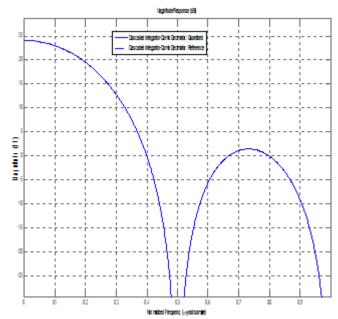

Figure 3: Maximum attenuation at the edge of the useful signal bandwidth

The main parameters that characterize the comb filter performances are the passband droop and the selectivity factor

## 3. Various Methods used for Compensation of **CIC Decimation Filter**

(A) CIC Roll-Off Compensation filter: In this method, we compensates the roll off of the CIC filter in pass band by letting the CIC filter followed by a symmetric FIR filter with a minimum order. The coefficients of the compensation filter are given by-

$$\left[\frac{-a}{1-2a'}\frac{1}{1-2a'}\frac{-a}{1-2a}\right] \tag{3}$$

The performance of the compensation filter depends on the value of a, which is obtained by minimizing the corresponding error function. CIC roll off compensation

$$c(n) = \frac{-a}{1-2a} \delta(n+1) + \frac{1}{1-2a} \delta(n) + \frac{-a}{1-2a} \delta(n+1)$$

Where, a  $\neq 0.5$

Frequency response  $C(\omega)$  of the CIC roll off compensation

filter C (n) is:

$$C(\omega) = \frac{1 - 2a\cos\omega}{1 - 2a} \dots \dots 5(b) \quad a \neq 0.5$$

Error function is defined by

Error function is defined by

$$E_{uw(\alpha)} = \int_{0}^{P_{e}} \left( D(\omega) - c(\omega) f(\omega) \right)^{2} d\omega$$

Where, Pe is pass band edge of the received signal.

In case of using the weighting function w (\omega), the error function is given by

$$E_{(a)} = \int_{0}^{\infty} (D(\omega) - c(\omega)f(\omega))^{2} W(\omega)d\omega$$

$$a = \frac{\int_0^{\pi} f(\omega) (1 - \cos \omega f(\omega)) (1 - f(\omega)) W(\omega) d\omega}{\int_0^{\pi} f(\omega) (1 - \cos \omega f(\omega)) (1 - \cos \omega) W(\omega) d\omega}$$

SNR (dB), are 2, 2 times, -37.56dB, 0.1458. It slightly improves the flatness of the pass band. It requires at least two multipliers. Better compensation in the wideband.

#### (B) Compensated CIC-Cosine decimation filter

Transfer function of compensation filter is given as

$$H_{comp}(z^{M}) = a + bZ^{-M} + aZ^{-2M}$$

(4)

Where a & b are real valued constant, and M is decimation factor

Magnitude response is:

$$|H_{comp}(e^{jM\omega})| = |2a\cos(M\omega) + b|$$

(5)

Worst pass band distortion occurs at  $\omega = 0 \& \omega = \omega_c$ Where,

$$\omega_c = \frac{\pi}{MR}$$

R is the decimation factor of next decimation stage.

$$\omega = 0 , 2a + b = 1$$

(6)

In order to compensate the pass band droop  $\delta c$  at the frequency  $\omega_c$

$$2\cos(M\omega_c) + b = \frac{1}{\delta_c}$$

(7)

$$\delta_{\rm comp} = \frac{1}{\delta_{\rm z}} \tag{8}$$

$$\begin{bmatrix} \mathbf{2} & \mathbf{1} \\ \mathbf{2}\cos(M\omega_c) & \mathbf{1} \end{bmatrix} = \begin{bmatrix} \mathbf{1} \\ \boldsymbol{\delta}_{comp} \end{bmatrix}$$

(9)

$$\begin{bmatrix} a \\ b \end{bmatrix} = \begin{bmatrix} \frac{-1}{2(cos(M\omega_c)-1)} & \frac{1}{2(cos(M\omega_c)-1)} \\ \frac{cos(M\omega_c)}{(cos(M\omega_c)-1)} & \frac{-1}{(cos(M\omega_c)-1)} \end{bmatrix} \begin{bmatrix} 1 \\ \delta_{comp} \end{bmatrix} \label{eq:delta_cos}$$

(10)

$$a = \frac{-1 + \delta_{\text{comp}}}{2(\cos(M\omega_c) - 1)}$$

$$b = \frac{\cos(M\omega_c) - \delta_{comp}}{\cos(M\omega_c - 1)}$$

(11)

The respective values of M, K, R are 4, 4, 8

$$\omega_c = \frac{\pi}{MR} = \frac{\pi}{4X8} = 0.09817477$$

$$\delta_{comp} = \frac{1}{\delta_c} \& \delta_c < 0.01 \text{ dB}$$

It is Multiplier free. There is a tradeoff between the desired compensation of the pass band droop. Filter coefficients can control the desired passband droop of the overall decimation filter. Rate becoming a second order filter .The magnitude response of (3) is expressed as:

### Volume 4 Issue 9, September 2015

$$|H_{comp}(e^{jM\omega})| = |2acos(M\omega) + b|$$

In order to compensate the passband droop  $\delta_c$  at the frequency  $\omega_c$ ,

$$\delta_{c} = \left| \frac{\sin M\pi fn}{M \sin(\pi fn)} \right|^{K}$$

(12)

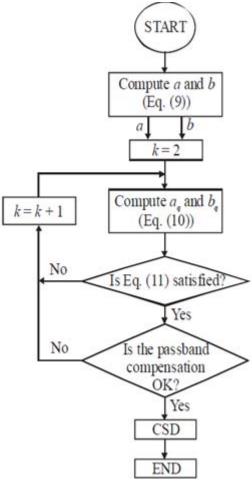

# 4. Block diagram of the Compensator Filter Design [5]

**Figure 5:** Block diagram of the compensator filter design [5]

#### (C) Passband droop correction

The transfer function of the proposed compensation filter is given by:

$$\mathbf{H}_{\text{comp}}(\mathbf{z}^{\mathbf{M}}) = \mathbf{a} + \mathbf{b}\mathbf{Z}^{-\mathbf{M}} + \mathbf{a}\mathbf{Z}^{-2\mathbf{M}}$$

Where, a and b are real valued constants and M is a decimation filter. Using multirate identity this filter can be moved to a low rate which is a M times less than high input

#### 5. Results

#### MATLAB Exercises- it contains the following matter

- FDATOOL Exercises (Graphs)

- Programming code (CIC low pass filter, inverse sinc , cascaded form CIC )

- Programming code (CIC low pass filter, high pass filter, cascaded form CIC)

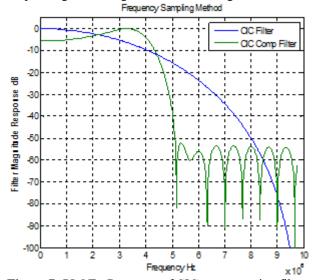

Now using the proposed method coefficients of compensated filter is calculated and frequency response is plotted.

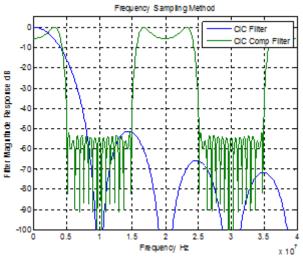

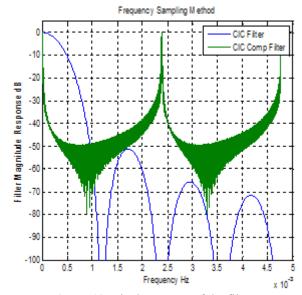

**Figure 6:** Frequency response of CIC filter is calculated according to the given values

| A | -0.011288673 |

|---|--------------|

| В | 1.022577348  |

Finally cascading of CIC filter and compensation filter is made and frequency response is accordingly plotted

The respective values of M, K, R,  $\Omega$ p, fp are 4, 4, 8,0 .09817477, 0 .015625

This procedure is programmed in MATLAB, and the corresponding block diagram is shown in Fig.

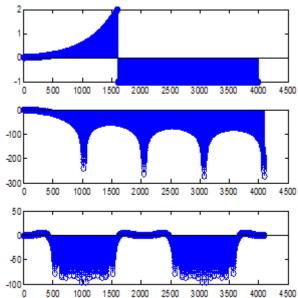

Figure 7: PLOT - Response of CIC compensation filter

Figure 8: PLOT - Complete response of CIC compensation filter.

#### (B) Programming view

Figure 9: Programming Code View of (CIC Low Pass Filter, Inverse Sinc, Cascaded form CIC)

Figure 10: Final response of the filter

#### 6. Conclusion

Responses are given using FDA Tools and programming code on MATLAB. Here we used three coefficients so less computation is required. The programming code is valid for in general for optimum values of decimation factor & no of stages. the appropriate graphs are shown. In case of more passband droop then we use the filter of more than one. The second programming code is based on cascading process of CIC low pass filter with high pass filter

## 7. Acknowledgements

It gives me immense pleasure and satisfaction to express my heart-felt gratitude to my guide Mr. Kamal Prakash Pandey for accepting me as his project student and providing me with excellent guidance and constant encouragement throughout my project duration. A wonderful work place provided by advanced VLSI lab in SIET ALLAHABAD.

#### References

- [1] ECTI TRANSACTIONS ON COMPUTER AND INFORMATION TECHNOLOGY VOL.4, NO.1 MAY 2010 Compensated CIC-Cosine Decimation Filter Gordana Jovanovic Dolecek and Fernando Javier Trejo

- [2] Introduction of CIC ,Altera application note no.455

- [3] Understanding cascaded integrator-comb filters By Richard Lyons Embedded Systems Design.

- [4] E. B. Hogenauer, —Areconomical class of digital filters for decimation and interpolation", IEEE Transactions on Acoustics, Speech and Signal Processing, Vol. 29, No. 2, pp. 155–162, 1981.

- [5] S. K. Mitra, —Digital Signal Processing—A Computer Based Approach", Second Edition, McGraw-Hill, 2001.

- [6] H. Aboushady, Y. Dumonteix, M. M. Louerat and H. Mehrez, -Efficient polyphase decomposition of comb decimation filters in Sigma-Delta analog-to-digital converters", IEEE Transactions on Circuits and Systems IIAnalog and Digital Signal Processing, Vol. 48, No. 10, pp. 898 - 903, 2001.

- [7] Gordana Jovanovic-Dolecek and Sanjit K Mitra, -On Design of CIC Decimation Filter with Improved Response", IEEE 3rd International Symposium on Communications, Control and Signal Processing, pp. 1072 - 1076, 2008.

- [8] Gordana Jovanovic Dolecek and Fred Harris, —Deign of CIC Compensator Filter in a Digital IF Receiver", IEEE International Symposium on Communications and Information Technologies, pp. 638 - 643, 2008.

- [9] Ljiljana Milić, -Multirate Filtering for Digital Signal Processing: MATLAB Applications", Information Science Reference, First Edition, 2009.

- [10] Rozita Teymourzadeh and Masuri Othman, -VBI Implementation of Cascaded Integrator Comb Filters for DSP Applications", 4th National Technical Postgraduate symposium, 2006.

- [11] Xilinx, Inc., -Virtex-V platform FPGA handbook", Vol. 3, No. 1, 2012.

## **International Journal of Science and Research (IJSR)**

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

## **Author Profile**

**Rajesh Kumar Dubey** doing M.TECH 2<sup>nd</sup> year in (VLSI DESIGN) form SIET Allahabad.

Kamal Prakash Pandey is Associate Prof. at SIET, Jhalwa-Allahabad. He obtained B.E. (Electronics and Communication Engg.) from MMMEC, Gorakhpur M.Tech. from NIT Kurukshetra Haryana, formerly known as Regional Engg. College Kurukshetra

Haryana. His area of interest includes digital electronics, VLSI Technology and Design and integrated circuits. He has published books on integrated circuits and electronics engineering.