# Design of Wallace Tree Multiplier using Adiabatic Logic

Bhushan V. Mude<sup>1</sup>, Prof. R. N. Mandavgane<sup>2</sup>, Prof. A. P. Bagde<sup>3</sup>

<sup>1</sup>M.Tech (IV SEM), VLSI, BDCE, Sewagram, Wardha, India

<sup>2</sup>Associate Professor and Head, Department of E&T Engineering, BDCE, Sewagram, Wardha, India

<sup>3</sup>Assistant Professor Department of E & T Engineering, BDCE, Sewagram, Wardha, India

Abstract: Wallace Tree Multiplier (WTM) is one of the fastest multiplier used in many data-processing processors to perform fast arithmetic functions. From the structure of the RCWM (Reduced Complexity Wallace Tree Multiplier), it is clear that there is scope for reducing the area and power consumption. This work uses a simple and efficient gate-level modification to significantly reduce the area and power of the WTM. Conventional WALLACE TREE MULTIPLIER (WTM) is still area-consuming due to the CMOS switching structure. The excessive area overhead makes WTM relatively unattractive but this has been circumvented by the use of Adiabatic Logic introduced. The logic operations involved in conventional RCWM (Reduced Complexity Wallace Tree Multiplier) and Wallace Tree Multiplier (WTM) are analyzed to study the data dependence and to identify redundant logic operations. Reduced complexity Wallace multiplier (RCWM) reduced number of half adders used in Standard Wallace Multiplier (SWM) with a slight increase in full adders to reduce the number of gates. Adiabatic Logic eliminated all the redundant logic operations present in the conventional RCWM (Reduced Complexity Wallace Tree Multiplier). Experimental analysis shows that this architecture achieves the three folded advantages in terms of area and power.

Keywords: Wallace tree multiplier, adiabatic logic, tanner tool, 4×4 multiplier

### 1. Introduction

Multipliers are one the most important component of many systems. In high speed digital signal processing (DSP) and image processing multiplier play an vital role. In image processing fast Fourier transform (FFT) is one of the most important transform often used. A computational process of fast Fourier transform requires large number of multiplication and addition operation. The execution of these algorithms requires dedicated MAC and Arithmetic and Logic Unit (ALU) architectures. Multipliers and adders are the key element of these arithmetic units as they lie in the critical path. With the recent advances in technology, many researchers have tried to implement increasingly efficient multiplier. They aim at offering low power consumption, high speed and reduced delay.

One such multiplier is Standard Wallace Multiplier (SWM). SWM is fully parallel version of the multiplier, the carry save adders used in SWM are conventional full adders whose carries are not connected, so that three inputs are taken and two words are out. SWM also uses half adders in reduction phase. A Wallace Multiplier is an easily hardware implementable and efficient methodology, that multiplies two integers, proposed by an Australian Computer Scientist Chris Wallace. For unsigned multiplication, up to n shifted copies of the multiplicand are added to form the result. The entire procedure is carried out into three steps: partial product (PP) generation, partial product grouping & reduction, and final addition.

The principle of Wallace tree multiplication. For an n x n multiplication there are n2 partial products that have to be summed. The 1st step in the algorithm involves grouping the partial products into sets of 3. For example, if there are n' rows of partial products, 3\*[n/3] rows are grouped and

the remaining n mod 3 rows are passed to the next stage. Therefore three rows of partial products are grouped together in stage 1, These 3 rows are then sum using full adders and if there are 2 dots in particular column half adders are used. The resulting sum and carry signals from the half and full adders are passed to the next stage. The process is repeated till the entire n partial products are summed. The resulting sum and carry out of the last stage is added using a fast carry propagation adder at the final stage.

Reduced complexity Wallace multiplier (RCWM) [1] reduced number of half adders used in SWM with a slight increase in full adders to reduce the number of gates. Reduced complexity Wallace Multiplier (RCWM) is the modified version of Standard Wallace Multiplier (SWM). In SWM they use full adder and half adder in their reduction phase, but half adder do not reduced the number of partial bit, therefore RCWM reduced the number of half adder used in the SWM with slightly increase in full adder . The partial products are formed by N2 AND gates. The partial products are arranged in a Tree structure format. The modified Wallace reduction method divides the matrix into three row groups. Full adders are use for each group of three bits in a column like the Standard Wallace reduction. A two bits group in a column is not processed, so it is passed on to the next stage (in contrast to Standard Wallace method). Single bits are passed on to the next stage as in the Standard Wallace reduction. The only time half adders are used is to ensure that the number of stages does not exceed that of a Standard Wallace multiplier. For some cases, half adders are used in the final stage of reduction. In RCWM they use carry propagating adder (CPA). One possible carry propagating adder for RCWM is a hybrid adder consisting of S+1 ripple carry half adder.

Both the multipliers SWM and RCWM have same number of stages and delay is also same. In Energy Efficient CMOS full adder in reduced complexity Wallace Multiplier at the place of Full adder of standard Wallace Multiplier in order to reduce Area, Power and improvement in speed. An Energy Efficient CMOS Full adder design using alternative logic scheme gives low power delay product (PDP), in terms of speed, power consumption and reduced area. This paper proposes use of new Energy Efficient switching method that is Adiabatic switching for CMOS full adder in reduced complexity Wallace multiplier in order to reduce power even further.

Adiabatic Logic is the term given to low-power electronic circuits. The problem of energy dissipation in smaller and faster circuit is solved by Adiabatic logic. The main causes of energy dissipation in CMOS circuits is due to the charging and discharging of the node capacitor. In adiabatic switching, the process of charging and discharging the node capacitances is carried out in a way so that a small amount of energy is wasted and a recovery of the energy stored on the capacitors is achieved. Adiabatic switching can be achieved by ensuring that the potential across the switching devices is kept arbitrarily small. This can be achieved by charging the capacitor from a time varying voltage source or constant curent source.

## 2. Literature Review

1. Authors Shahebaj Khan, Sandeep Kakde, Yogesh Suryawanshi proposed a technology entitled "VLSI Implementation of Reduced Complexity Wallace Multiplier Using Energy Efficient CMOS Full Adder" in which modified reduced complexity Wallace Multiplier with reduced power consumption and area by using Energy Efficient CMOS Full Adder at the place of conventional Full adder is presented. From the literature view it can be seen that proposed multiplier reduced power and total number of gate count i.e. area is reduced.

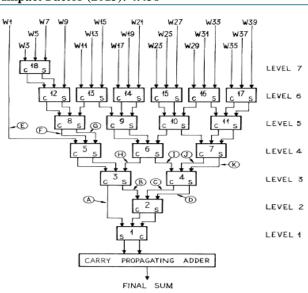

2. Author C. S. WALLACE et.al. in this paper suggested a technology for multiplier entitled "A Suggestion for a Fast Multiplier" suggest A Multiplier is an easily hardware implementable and efficient methodology, that multiplies two integers. For unsigned multiplication, up to n shifted copies of the multiplicand are added to form the result. The entire procedure is carried out into three steps 1.partial product (PP) generation 2.partial product grouping & reduction 3.final addition. The following diagram shows the adder tree design by Wallace.

3. Authors Kazunari Kato, Yasuhiro Takahashi, and Toshikazu Sekine in paper entitled "Two Phase Clocking Sub threshold Adiabatic Logic". They propose a novel sub-threshold adiabatic logic. Our previously proposed ultra-low power sub threshold adiabatic logic has been a problem that noise margin is reduced, so that it is impossible to implement a cascade connection. In this paper, they propose a novel sub-threshold adiabatic logic. To evaluate their proposed circuit, a half adder, full adder, dynamic flip flop and  $4\times4$  array multiplier are designed, and then the operation function and power dissipation are confirmed. From the simulation results, the power dissipation of the proposed multiplier is lower than that of the conventional CMOS.

4. Author Nazrul Anuar, Yasuhiro Takahashi, and Toshikazu Sekine in paper entitled "4-bit Ripple Carry Adder using Two Phase Clocked Adiabatic Static CMOS Logic" proposed the low energy operation of 4-bit ripple carry adder (RCA) employing two phase clocked adiabatic static CMOS logic (2PASCL) circuit techniques. They evaluate NOT, NAND, XOR and NOR logic gates on the basis of the 2PASCL topology using SPICE implemented using 0.18 m CTX CMOS technology. For NOT circuit, the analytical and simulation values are compared. By removing the diode from charging path, the higher output amplitude is achieved and the power consumption of the diode is eliminated. From the simulation results, they noticed that 4bit 2PASCL RCA can save an average of 71.3% of dissipated energy as compared to that with a static 4-bit CMOS RCA at transition frequencies of 10 to 100 MHz. The results indicate that 2PASCL technology can be advantageously applied to low-power digital devices operated at low frequencies, such as radio-frequency identifications (RFIDs), smart cards, and sensors.

5. Authors M. Chanda, A. Dandapat, Toshikazu SekineH. Rahamanin paper entitled "Ultra Low-Power Sequential Circuit Implementation by a Quasi Static Single Phase Adiabatic Dynamic Logic (SPADL)" proposed Implementation of sequential logic circuits by using a novel Quasi-Static Single-phase Adiabatic Dynamic Logic (SPADL) has been presented. SPADL uses only a single sinusoidal source as supply-clock. This not only ensures lower energy dissipation, but also simplifies the clock design which would be otherwise more complicated due to the signal synchronization requirement. Simplicity and static logic resembled characteristics of SPADL logic, substantially decreases circuit complexity with improved driving ability and circuit robustness.

# 3. Proposed Work

Figure: Wallace Tree Multiplier

Wallace multipliers act in three stages:1)Generate all bits of the partial products in parallel. Collect all partial products bits with the same place value in bunches of wires and reduce these in several layers of adders till each weight has no more than two wires. For all bit positions which have two wires, take one wire at corresponding place values to form one number, and the other wire to form another number. Add these two numbers using a fast adder of appropriate size.

We assume that Full adders and half adders will be used. A full adder takes 3 inputs and produces one output of the same weight (sum) and another of higher weight (carry). This is called a (3,2) adder. It reduces the number of wires at its own weight by 2 and adds one wire at the higher weight. A half adder takes 2 inputs and produces one output of the same weight (sum) and another of higher weight (carry). This is a (2,2) adder. It reduces the number of wires at its own weight by 1 and adds one wire at the higher weight. The reduction algorithm is general and can be used with any adders of type (n, m). For example, a carry save adder is of type (4, 2).

Each reduction stage looks at the number of wires for each weight and if any weight has more than 2 wires, it adds a layer of adders. When the numbers of wires for each weight have been reduced to 2 or less, we form one number with one of the wires at corresponding place values and another with the other wire (if present). These two numbers are added using a fast adder of appropriate size to generate the final product.

At any layer, if we find 3 wires for any weight, we place a Full Adder, which generates 1 wire of the same weight and 1 wire with the next higher weight. We place enough full adders in this layer such that the remaining wires for any weight are less than 3. If only one wire is left, it is carried through to the next layer. If there are two wires left after

using Full Adders for all groups of 3, we have the option of either passing them both through to the same weight or to pass 1 wire to the same weight and the other to the next higher weight (using a Half Adder). Different rules apply for the last reduction step and the earlier ones.

Bits on the right with no in-coming carry are reduced with a half adder. This reduces the size of the final adder as single wires will be left for bits on the right. If this is not the last layer and the next layer will have In-coming carry wires, we pass through the 2 wires if it will make the number of output wires at this weight a multiple Of 3. Otherwise, we place a half adder. The reduction procedure is carried out for all weights. Starting from the least significant weights. At the end of each layer, we count wires for each weight again, and if none has more than 2 wires, we proceed to the final addition stage. If any weight has 3 or more wires, we add another layer, and repeat this procedure till the number of wires for all weights is reduced to 2 or less. Now we compose one number from one of the left over wires at corresponding weights and another from the remaining wires. Finally, we use a conventional fast adder of appropriate size to add the two number.

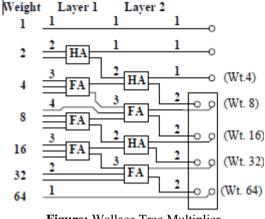

Consider a multiplier for 4X4 bits. Partial products are generated in parallel and we have the following wires:

| Weight | Terms                | Wires |

|--------|----------------------|-------|

| 1      | a0b0                 | 1     |

| 2      | a0b1, a1b0           | 2     |

| 4      | a0b2, a1b1, a2b0     | 3     |

| 8      | a0b3, a1b2 a2b1 a3b0 | 4     |

| 16     | a1b3, a2b2, a3b1     | 3     |

| 32     | a2b3, a3b2           | 2     |

| 64     | a3b3                 | 1     |

# 4. Implemented Work

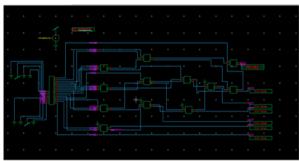

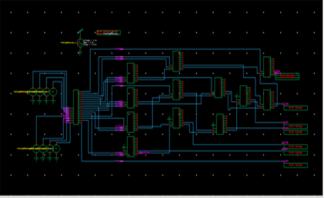

Figure: conventional RCWTM without Adiabatic

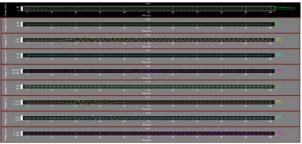

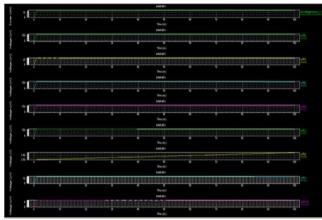

Figure: Waveform of conventional RCWTM without Adiabatic

Figure: RCWTM using Adiabatic Logic

Figure: Waveform of RCWTM using Adiabatic Logic

## 5. Comparison Table

COMPARISION TABLE BETWEEN POWER AND CURRENT OF RCWTM AND RCWTM USING ADIABATIC LOGIC

| PARAMETER | RCWTM        | RCWTM (ADIABATIC) |

|-----------|--------------|-------------------|

| CURRENT   | 104.41593 uA | 6.83052 nA        |

| POWER     | 313.24780 uW | 17.07630 nW       |

## 6. Conclusion

The CMOS Switching method for designing low voltage and low power Wallace Tree Multiplier has been presented. The proposed Adiabatic Switching structure and the RCWM to benefit the high speed and low power. A simple approach is proposed in paper to reduce the area and power of RCWM. This new switching technique offers the great advantage in the reduction of area and also the total power. In this paper, energy efficient Reduced Complexity Wallace Tree Multiplier Proposed. By the process of charging and discharging the node capacitances is carried out in a way so that a small amount of energy is wasted and a recovery of the energy stored on the capacitors is achieved.. They have analyzed the Adiabatic switching can be achieved by ensuring that the potential across the switching devices is kept arbitrarily small. This can be achieved by charging the capacitor from a time varying voltage source or constant curent source. Due to the small area required for adiabatic switching this multiplier is high speed, low area and very low power multiplier.

### References

- [1] Shahebaj Khan, Sandeep Kakde, Yogesh Suryawanshi, "VLSI Implementation of Reduced Complexity WallaceMultiplier Using Energy Efficient CMOS Full Adder", 978-1-4799-1597-2/13 ©2013 IEEE

- [2] C. S. WALLACE, "A Suggestion for a Fast Multiplier", IEEE TRANSACTIONS ON ELECTRONIC COMPUTERS.

- [3] Kazunari Kato, Yasuhiro Takahashi, and Toshikazu Sekine, "Two Phase Clocking Subthreshold Adiabatic Logic", 978-1-4799-3432-4/14 ©2014 IEEE

- [4] Nazrul Anuar, Yasuhiro Takahashi, and Toshikazu Sekine, "4-bit Ripple Carry Adder using Two Phase CMOS Clocked Adiabatic Static Logic", 978.1.4244.4547.9/09 c 2009 IEEE

- [5] M. Chanda, A. Dandapat, Toshikazu SekineH. Rahamanin, "Ultra Low-Power Sequential Circuit Implementation by a Quasi Static Single Phase Adiabatic Dynamic Logic (SPADL)", 978-1-4244-4547-9/09 ©2009 IEEE

- [6] S.Kim and M.C.Papaefthymiou . "Single-phase sourcecoupled adiabatic logic," in Proc. Int. Symp. Low-Power Electron. Design, San Diego, CA, Aug. 1999, pp. 97–99.

- [7] H.Mahmoodi-Meimand A.Afzali-Kusha and . M.Nourani, "Adiabatic carry look-ahead adder with efficient power clock generator," IEEE Proc.-Circuits Devices Syst., Vol. 148, No. 5, Oct 2001

- [8] Mohamed Asan Basiri M, Samaresh Chandra Nayak, Noor Mahammad Sk, "Multiplication Acceleration Through Quarter", 978-1-4799-2866-8/14@2014 IEEE

## **Author Profile**

Mr B. V. MUDE received the Bachelor of Engineering degree in Electronics and Comm. Engineering from R.T.M. Nagpur University, Wardha in 2012 and pursuing his M.Tech in VLSI from B. D. College of Engineering, Wardha, R.T.M. Nagpur University. He is working towards M.Tech research project at R.T.M. Nagpur University. He is currently working as a Lecturer in Electronics Engineering Department at S. D. College of Engineering, Selukate Wardha. His area of interests include VLSI design and optimization.

Mrs. Rajashree N. Mandavgane received her B.E degree and M.Tech degree from R.T.M.N.U University, Maharashtra, India. She is presently working as Associate Professor and Head in the department of Electronics and Tele-Communication

Engineering, at B. D. College of Engineering, sewagram Wardha. She is having a total 23 years of teaching experience. With a subject specialization in general and digital electronics.