# Software Defined Radio Signal Detector Implementation using FPGA

## Rohan Fernandes<sup>1</sup>, Shubhangi Mahamuni<sup>2</sup>

<sup>1</sup> Research fellow, Department of Electronics, MIT Academy of Engineering, Pune, Maharashtra, India

<sup>2</sup> Assistant Professor, Department of Electronics and Telecommunication, MIT Academy of Engineering, Pune, Maharashtra, India

**Abstract:** Signal detection is the very critical task upon which the entire operation of the radio device rests. Software-Defined Radio (SDR) is a technology that most of traditional radio applications are implemented in software. It has the advantages like reconfigurability and flexibility, SDR system has to face a critical challenge of realtime processing due to high sampling rates and latency. Signal detection methods in radio signal detection has gained new aspects with awareness of cognitive radio systems. The requirement of spectrum sensing has been eliminated recently by FCC. The objective is to increase the bandwidth, keep low latency and reduce the power consumption without reducing the flexibility of a software radio. The implementation of signal detector on FPGA would reduce the power consumption due to signal processing done on a software defined radio by a host computer and increase data rate of a software radio. This is justified by developing application of aircraft tracking and FM.

Keywords: FPGA, SDR, Cognitive radio, Low power.

## 1. Introduction

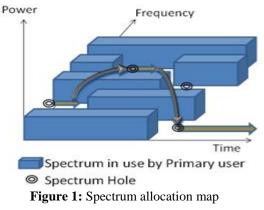

Spectrum scarcity is a serious worldwide concern today. The majority of RF spectrum is already allocated and obtaining new blocks of frequency at affordable costs is often infeasible. While these frequencies are actually licensed, the licensed users or primary users (PUs) do not continuously transmit in their respective bands [1]. This is an opportunity for the reuse of the licensed but vacant spectrum, for which new techniques and tools must be devised. The rapidly emerging field of cognitive radio (CR) is one enabling technology that allows secondary or cognitive radio users to transmit when the spectrum is judged to be available, without interfering with the ongoing transmission of the PUs [2]. In figure 1, we show a representative diagram of five PU's and the time / frequency map of the RF transmissions of this PU. It can be observed that there are "white spaces" where the PU's are not emitting RF energy, which we call spectrum holes. An interesting and challenging responsibility of a CR is locating and cataloging PUs. This is achieved by spectrum sensing already. In 2008 the requirement of spectrum sensing has been eliminated recently by FCC [4]. To the best of our knowledge this is the first paper presenting hardware implementation of spectrum sensing algorithm which makes it possible to achieve appreciable reduction in power dissipation without compromising the performance and sensing ability of a radio device.

The power consumed by a software defined radio is enormous, as all the signal processing and detection is done on the host computer.

This power minimization problem can be solved by developing signal detection and identification algorithm which can be totally be implemented on a hardware. This can be achieved by implementing a combined algorithm, energy detector [5] for detection of spectrum occupancy and cyclostationary detector for detection of pattern of the wave received and its type of user detection (Primary or secondary).

The newly available RTL-SDR devices have low latency, consume low power and the loss of data is also low. However the band width and the available features can be improved without changing the features of the RTL-SDR device.

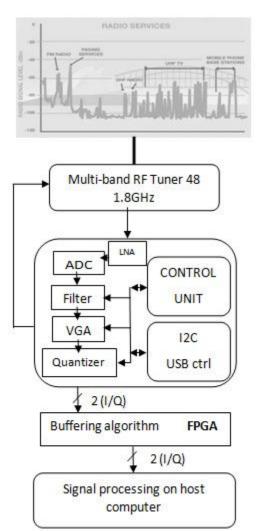

This algorithm is hardware implementation for signal detection and further communication process to be done by the host computer as represented in fig 2.

This paper is divided into three parts initially the implementation on a FPGA, Secondly aircraft tracking application and lastly the combined process and its power and silicon area usage on a FPGA.

## 2. Implementation

Most of the power in a software defined radio is utilized for the spectrum sensing and signal detection algorithms on the host computer. Usually these devices have high end processors consuming high power. Utilizing these devices for signal detection and signal processing is not appreciable. Developing a dedicated hardware for signal detection will be an appropriate solution. The available algorithms can be implemented on a FPGA or by using a DSP. FPGA's have fine granular advantage and reconfigurable capability, allowing more simplification and speed to the signal processing.

PE =

$$\frac{1}{N} \sum_{n=0}^{N-1} |\mathbf{x}(n)|^2$$

..... Equation 1

The signal to be detected is sensed by energy detector algorithm for an initiated signal in the spectrum. This sensed signal may be of any radio service irrespective of the service we desire. This distinguishing of required service and received service is done by the cyclostationary algorithm [6]. The patterns for a certain service consists of a cyclic prefix etc.; the ideal patterns can be stored in LUT's on a FPGA, used for autocorrelation with the received signal and the service can be distinguished from unnecessary services and the spectrum user type can be easily determined. This combined algorithm implementation on a FPGA allows further upgrade of the more pattern for different environments of radio service.

Figure 2: Signal detector block diagram

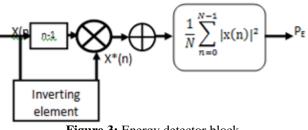

#### A.Energy detection on a FPGA.

The energy detection algorithm [5] block diagram which can be implemented on a FPGA is presented in Fig. 3 It consists of two multipliers to perform operations on both real and imaginary signals and a digital integrator (summation product). The energy detector is the simplest signal detection algorithm on hardware and less complex then other implementations. Its power consumption is maximum contributed by the multipliers for computing the square of the absolute value of the input signal in equation 1.

Figure 3: Energy detector block.

#### B. Cyclostationary pattern reorganization on a FPGA.

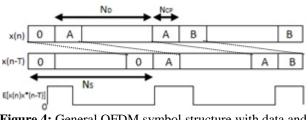

The typical structure of an OFDM symbol is as shown in Fig. 4 The OFDM symbol with a length Ns, consists of the actual data contents having a length  $N_{D}$  and a cyclic prefix having length  $N_{CP}$ . This cyclic prefix is a copy of  $N_{CP}$  denoted as 'A' in the figure. Samples from the end of the symbol are added to the front of the symbol in order to reduce inter-symbol-interference and improve the system performance in a multipath propagation environment. The cyclic prefix can also be used for synchronization [7].

Figure 4: General OFDM symbol structure with data and cyclic prefixes

The resemblance of the signals between available ideal signal pattern and the received signals can be done by using cross-correlation between the signals. The correlation function can be computed as,

$$A_{x(n)x_i(n)} = \frac{1}{N} \sum_{\tau=0}^{n} x(n) x_k^* (n-\tau).$$

Equation 2

K = 0, 1, 2, 3...k

This algorithm is most suitable for implementation on FPGA. We need to have database of the prefix of the various services this can be done by the LUT's banks available on FPGA. The signal rate is high for the received signal; this has to be in a FIFO for successive samples of the signal of neighboring frequencies.

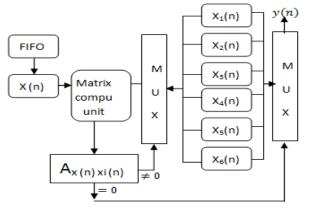

The signal x(n) is then cross correlated with signals  $x_1(n)$ ,  $x_2(n)$ ,  $x_3(n)$ ,  $x_4(n)$ ,... $x_T(n)$ ; respectively as represented in Figure 5. This is achieved by using matrix convolution method as the signals have both real and imaginary components. The imaginary components can be further derived from equation 2 as,

$$A_{x(n)x_i(n)} = \frac{1}{N} \sum_{n=0}^{N-1} x(n) + j y_k(n) \dots Equation 3$$

= X + jY\_k \cdots Equation 4

A complex matrix can be formed by using the above equation, with opposite elements the conjugate of each other i.e;  $A_{ij}$ = - $A_{ji}$ . Output of the cyclostationary block is the signal whose correlation is below threshold point (ideally = 0).

Paper ID: SUB155874

The service of the signal can be detected by this cyclostationary block. For a dedicated service application the service for which the signal has to be detected is the only correlation factor for the detected signal.

Figure 5: Cyclostationary block.

#### C.Power consumptions and logical hardware resource utilization.

The implementation of the signal detection algorithm on a FPGA reduces power consumptions as power consumed by high end processors on a software radio device is high [8]. This hardware implementation is simplified and simulated Spartan 6 FPGA on Xilinx.

## **D.** Experimentation.

The device contains three components

(1) The Tuner (Raphael Micro R820T radio tuner) and

(2) An 8-bit ADC and USB data pump (Realtek RTL2832U)

(3) FPGA spartan 6 board.

The tuner chip serves as the radio frequency (RF) front-end for the SDR. Following a miniature coax connector for the antenna is a low noise amplifier (LNA) providing a noise figure (NF) of about 3.5 dB. The tuning range of the R820T is 24 MHz to 1850 MHz. In the RTL2832U digital signal processing (DSP) takes place this includes additional filtering and down sampling of the IF signal initially delivered by the R820T. The ADC on RTL2832U produces 8-bit real/inphase (I) and imaginary/quadrature (Q) interleaved sample values, in an unsigned format. The sample they are finally converted to signed 8-bit values and parallel I and Q streams are available at the Output. The signal conversion, detection and buffering implementation is done on the FPGA. The RS232 HDL module available at http://www.ics.uci.edu/ is used to communicate with the host computer.

|   | Current | Aircraft ID | Flight ID | Latitude(deg) | Longitude(deg) | Altitude(ft) | Speed(knots) | Direction | U/D  |

|---|---------|-------------|-----------|---------------|----------------|--------------|--------------|-----------|------|

| 1 |         | 800400      | AIC513    | 18.4106       | 73.8407        | 12150        | 336          | S (162)   | 1344 |

| 2 |         | 8005DE      | IG0134    | 18.8247       | 74.0095        | 13025        | 352          | NE (33)   | 3072 |

| 3 |         | 80074D      |           |               |                |              | 427          | S (176)   | 0    |

| 4 |         | 70C0AD      | OMA822    | 17.7146       | 73.2353        | 41000        | 470          | NW (297)  | 0    |

| 5 | 1       | 80068B      | IGO407    | 18.5912       | 73.8101        | 5300         | 261          | W (275)   | 1728 |

| 6 |         | 896211      |           |               |                |              | 514          | NW (297)  | 0    |

Figure 7: Latency w.r.t. time plot.

To verify the theory aircraft deacon detection and decoding application is developed for an S-mode beacon. The decoding of s-mode signal have a fixed signal pattern as defined in aircraft collision avoidance system (ACAS). Mode-S signaling scheme has the following properties: Transmit Frequency: 1090 MHz Modulation: Pulse Position Modulation Data Rate: 1 Mbit/s Short Message Length: 56 microseconds

## Figure 6: Aircraft beacon decoding results

#### Long Message: 112 microseconds

Short messages contain the information like Message Type (Short or Long), Aircraft ID (Unique 24-bit sequence), CRC Checksum. Long messages contain all the information in a short message and optional information such as Altitude, Position, Direction and Velocity

| Project File:    | fifo_sdr.xise            | Parser Errors:        | No Errors   |  |

|------------------|--------------------------|-----------------------|-------------|--|

| Module Name:     | synced_fifo              | Implementation State: | Synthesized |  |

| Target Device:   | xc6sbx4St-3fgg484        | • Errors:             | No Errors   |  |

| Product Version: | ISE 13.2                 | • Warnings:           | No Warnings |  |

| Design Goal:     | Balanced                 | Routing Results:      |             |  |

| Design Strategy: | Xiinx Default (unlocked) | • Timing Constraints: |             |  |

| Environment:     | System Settings          | • Final Timing Score: | -           |  |

| Device Utilization Summ           | E    |           |             |

|-----------------------------------|------|-----------|-------------|

| Logic Utilization                 | Used | Available | Utilization |

| Number of Slice Registers         | 25   | 54576     | 0%          |

| Number of Slice LUTs              | 54   | 27288     | 0%          |

| Number of fully used LUT-FF pairs | 25   | 54        | 46%         |

| Number of bonded IOBs             | 22   | 296       | 7%          |

| Number of BUFG/BUFGCTRLs          | 1    | 16        | 6%          |

Figure 8: Design summary.

| Name         | Value   | 999,997 ps | 999,998 ps           | 1999,999 ps |

|--------------|---------|------------|----------------------|-------------|

| Ug clk       | 1       |            |                      |             |

| Un rst       | 0       |            |                      |             |

| 1 fifo_rd    | 1       |            |                      |             |

| 1 fifo_wr    | 0       |            |                      |             |

| 🏹 simulati   | 1       |            |                      | Ĩ           |

| 1 rom_rd_    | 0       |            |                      |             |

| 🕨 📲 rom_mei  | [11111, |            | [11111,0,110,1]      |             |

| ↓ rom_dat    | 110     |            | 110                  |             |

| le rom_ado   | 10      |            | 10                   |             |

| Te rom_cou   | 1111111 | 1111111111 | 11111111111111111111 | 1000111     |

| 🕨 📲 fifo_din | 0101101 |            | 01011010             |             |

| 🕨 📲 fifo_dou | 0010000 |            | 00100000             |             |

| 🗋 data_wi    | 1000    |            | 1000                 |             |

| 🛯 🔓 rom_size | 100     |            | 100                  |             |

|              |         |            |                      |             |

|              |         |            |                      |             |

Figure 9: VHDL design simulations.

| Table 1: | Result | obtained | by VHD | L design tools |

|----------|--------|----------|--------|----------------|

|----------|--------|----------|--------|----------------|

| Implementation  | Power   | Logic | Registers |

|-----------------|---------|-------|-----------|

| Energy detector | 2.82mW  | 612   | 290       |

| Cyclostationary | 32.38mW | 6779  | 1060      |

| FIFO            | 0.46mW  | 79    | 25        |

# 3. Conclusion and Result

The complexity of logic is based on the numbers reported by the design tool, includes the amount of a four-input LUT. The design tool reports the power consumed by the algorithm on watt. Table 1 shows the results obtained by VHDL design tools. Figure 6 shows the decoded aircraft beacon signals in real time which includes aircraft ID, Flight ID, latitude longitude, altitude, etc.

The latency is much higher than the traditional SDR for 2.5sec due to the use of FPGA in the path, after which the latency is constant and low as in the traditional SDR. The bandwidth is increased by 12 percent and the loss of packet is negligible and can be ignored.

# 4. Future Work

This device that is used for spectrum sensing in present applications merging this signal detection method will reduce device complexity and the power consumed by traditional SDR and the host computer together. With this implementation, software device independent signal detection standalone hardware can be developed as ready to use board for any cognitive radio communication device.

## References

- [1] J. Yang, "Spatial channel characterization for cognitive radios," MS Thesis, UC Berkeley, 2004.

- [2] I. F. Akyildiz, W-Y. Lee, and K. R. Chowdhury, "CRAHNs:

- [3] Cognitive Radio Ad Hoc Networks," Ad Hoc Networks Journal, (Elsevier), vol.7, no.5, pp. 810-836, July 2009.

- [4] Federal Communications Commission (FCC), "Notice of Proposed Rule Making," ET Docket no.06-156, October, 2006.

- [5] I. Kostylev, "Energy detection of a signal with random amplitude", in Proc. IEEE Int. Conf. on Commun. (ICC'02), New York City, New York, pp.1606–1610, May 2002.

- [6] Wen-jing Yue, Bao-yu Zheng, and Qing-min Meng, "Cyclostationary property based spectrum sensing algorithms for primary detection in cognitive radio systems," Journal of Shanghai Jiaotong University (Science), vol. 14, pp. 676-680, 2009, 10.1007/s12204-009-0676-0.

- [7] D. Tse and P.Viswanath, "Fundamentals of Wireless Communication." Cambridge, U.K.: Cambridge Univ. Press, 2005.

- [8] Jacques Palicot ,Xun Zhang,Pierre Leray, Christophe Moy Cognitive Radio and green communications: power consumption consideration SUPELEC/IETR, Cessonsévigné, France.

- [9] A. Puschmann, M. Kalil and A. Mitschele-Thiel., "Implementation and Evaluation of a Practical SDR Testbed", 4th International Conference on Cognitive Radio and Advanced Spectrum Management (CogART), 2011.

- [10] P.D. Sutton, J. Lotze, H. Lahlou, S.A. Fahmy, K.E. Nolan, B. Ozgul, T.W Rondeau, J. Noguera, L.E Doyle., "Iris: An Architecture for Cognitive Radio Networking Testbeds", IEEE Communications Magazine, vol. 48, 2010.

- [11] ANSI/IEEE std 802.11 part 11., "Wireless LAN medium access control (MAC) and Physical Layer (PHY) Specification", IEEE press, 1999.

- [12] Tahseen Flaih Hasan "FPGA Design Flow for SDR Transceiver using System Generator" International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-3, Issue-4, April 2014

# **Author Profile**

**Rohan Antony Fernandes** received B.E. from Dr.JJMCOE, Jaysingpur, India. Having teaching experience of 02 Years. Currently research fellow at Department of electronics, MIT Academy of engineering, Pune.

**Mrs. S. M. Mahamuni**, received M.E. from J. N. E. C. Aurangabad, India. Having teaching experience of 11 Years. She is currently assistant professor at MIT Academy of engineering, Pune. Registered for Ph.D. in wireless communication at SVNIT, Surat, Gujrat.

Currently working on BCUD funded Research project 11EG000378 titled "Spectrum Sensing in Cognitive Radio Network".