# FIR Interpolation Filter for Multi-Standard Digital Up Converter Using FPGA

# Chaithra M. R.<sup>1</sup>, Yashwanth N<sup>2</sup>

<sup>1</sup>PG Student, Department of ECE, Rajeev Institute of Technology, Hassan, Karnataka, India

<sup>2</sup>Assistant Professor, Department of ECE, Rajeev Institute of Technology, Hassan, Karnataka, India

Abstract: This paper proposes an implementation of pulse shaping FIR interpolation filter for digital up converter. The designing of root raised cosine FIR filter for multistandard DUC for different standards is reduces the multiplications and additions per input samples and reduction in the power consumption has also been achieved. The 2-bit binary common sub-expression (BCS) elimination method is used to design the multipliers so that the delay can be minimized with increased speed and power performance parameters. The design could be validated for a standard wireless communication technology with specific incoming bit streams. The proposed design could be implemented using RTL Code and functional correctness is verified using a sophisticated Modelsim/ISIM Simulator tool.

Keywords: Digital Up Converter, Software defined radio(SDR), Reconfigurable, Binary common sub-expression(BCS).

## **1. Introduction**

Filters are the primary elements of all signal dealing out and electronic systems. In digital signal processing systems most widely used operations are FIR filtering. FIR filters are the primary component of the Digital Up converter. In telecommunication industry, Software defined radio concepts for various data transfer rates and high channel capacities.SDR [2] is a single device that supporting present as well as upcoming standard available in wireless communication systems. In an SDR system, within a single chip multiple standards can be realized by providing the channel select filter at the input level. To meet the specifications like different channel bandwidths, sampling rates, carrier-to noise ratios, and interference profiles one reconfigurable sample rate converter is required. Some pulse shaping filters are used in sample rate converter to reduce the undesired production of aliasing and interference effect to shape this baseband signal. Reconfigurable interpolators can be used in a next generation transceiver to realize a variable sample rate converter in order to support different data rates of different multiple standards in a single terminal.

Pulse-Shaping FIR interpolation filter for digital up converter has been proposed by several researchers toward designing a low-power, low-area, and low-complexity reconfigurable channel filter for data rate conversion in SDR system. A multiplier-less FIR interpolator has been proposed in [3] with smaller area usage and reduction in power by using the efficient look up tables (LUTs). This architecture is undesired because of its large ROM size. Area-delaypower efficient FIR filter by distributed arithmetic computation is presented by Meher [4]. In this implementation reduction in memory size leads to increase in the delay and area, this not suitable for SDR system.

In common sub-expression elimination (CSE) [5] technique, multiplication operations are performed by shift and add operation, and this technique defines critical path of the circuit. The constant multiplications (CM) [6] technique is useful in implementing the higher order filter design for reducing the hardware usage. A low complexity based binary CSE (BCSE) algorithm has been proposed in [7]. Constant shift multiplication based FIR filter design has been proposed in [8] involves use of adders in the multiplier block. This uses an additional area and power, and hardware usage makes design is not suitable for SDR system. From this literature low complexity multiplier by which more area and power can be reduced in designing the digital up converter (DUC) for SDR system. This disadvantage can be overcome by RRC filter architecture; this technique initially reduces the multiplications and additions per input samples and reduces the hardware and power consumption with designing of 2-bit BCS technique.

## 2. Problems in Designing the Root Raised Cosine Fir Filter and Solution

#### A. Problems in Designing the RRC FIR Filter

The hardware implementation of a reconfigurable RRC FIR interpolation filter has the following challenges. Implementation of the FIR interpolation filters with different lengths requires interpolation factor and roll-off factor. Selections of these parameters for designing the filters are the major challenge. The total number of multipliers and structural adders will linearly increase with the number of parameters for designing the filter. As the number of multipliers and structural adders increases, hence the problem of area and power consumptions increases for implementing the variable length higher order filter in a single architecture.

In recent communication technologies software defined radio is one of the advent technologies used. These technologies pose a major challenge in terms of area power and speed. FIR filter designing plays a major role in designing Digital up converter in defining speed and power of any communication system. In BCSE technique, Proper choice of the length of the BCS is an important factor to avoid the inefficient utilization of hardware.

In BCSE technique, Proper use of BCS method to decrease the adders that maximizes the operating frequency of the filter is a challenge in the implementation of FIR filter for wireless communication standards. Propagation delay is another major tuning factor in defining the speed. The use of multipliers and adders with the conventional methods limits the speed and increases the power consumption of the system.

#### **B.** Solutions to the Problems

To solve the problems mentioned above proposed technique has the following steps.

- 1) The multiplexing technique can be used to decreasing the requirement of multipliers with control parameter (FTL\_SEL) for designing the filter is to be selected depending on the roll-off factor.

- 2) Coefficients are generated in MATLAB. These obtained coefficients are passed through another set of multiplexers, with interpolation factor. This technique reduces the number of additions and multiplications per input samples.

- 3) 2-bit BCSE technique has been used other than 3-bit BCSE technique, to reduce the critical depth. This method gives a good propagation delay as compared with 3-bit BCSE based design.

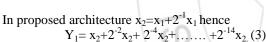

- 4) In an FIR filter, the multiplication operation between inputs and coefficients can be written as Y<sub>1</sub>=x<sub>1</sub>+2<sup>-1</sup>x<sub>1</sub>+2<sup>-2</sup>x<sub>1</sub>+.....+2<sup>-15</sup>x<sub>1</sub>(2)

This technique helps to reducing the hardware usage as well as area requirement.

# 3. Architecture of the RRC Filter

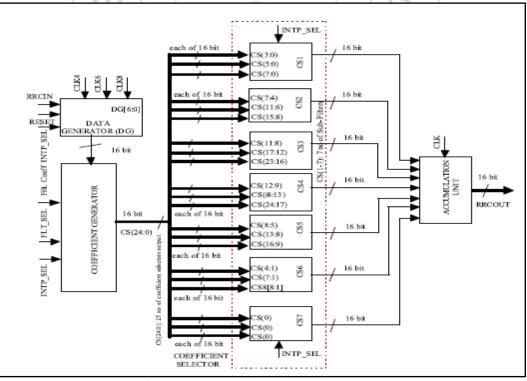

The proposed architecture of FIR interpolation filter block diagram is shown in Fig.1. In this architecture, two parameters interpolation factor and roll-off factors are used. And the CLK is used to sample the output (RRCOUT), operates at a higher rate than others. The proposed architecture consists of different modules, like data generator (DG), coefficient generator (CG), coefficient selector (CS), and an accumulation unit.

#### A. DG Block

In order to generate the data values for RRC filter based on the Clock signal and also sample the input data DG block is used depending on the interpolation factor selection value. Here the filter taps are selected with different interpolation factor.

## B. CG Block

In this block Multiplication between the obtained filterCoefficients from the MATLAB and the given inputs are performed. Coefficients are generated with Definite values of Roll-off factor, interpolation factor and sampling rate. Here the generated filter coefficients are 49-tap coefficients. Seven partial product outputs are generated and stored in different register blocks.

## C. Coefficient Selector Block

The CS Block is used to direct the proper data to the addition block by using multiplexer units. Multiplexer unit will select appropriate generated coefficients from Dg block. Addition of generated partial product values are performed by 2-bit BCSE method.

Figure 1: Proposed architecture of RRC filter

#### **D.** Accumulation Unit

This block has adders and registers blocks for addition and storing operation. The final output of RRC filter is generated in this block.

# 4. Results

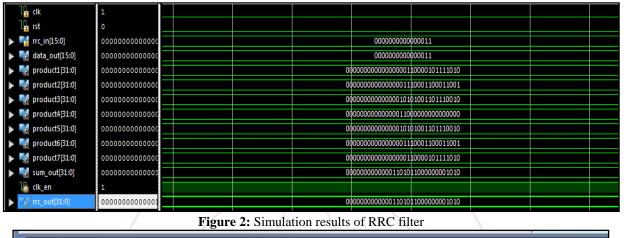

The simulation results of the proposed RRC filter is as shown in Fig.2. First data\_out signal is loaded by input value with enabling clock signal, then generated product values are added by using the 2-bit BCSE method, that is sum1=product1+product2, then

Sum1 value is added with product3 value. This method is continued to further steps. After that final rrc\_out value is loaded with sum\_out value. The chip scope results are matching with the simulation results so confirm that the implementation on FPGA is successful and the results are as per expectations. Fig.3 illustrates the chip scope results for proposed RRC filter module.

| Bus/Signal    | X    | 0    | 0 | 40 | 80<br> | 120 | 160  | 200    | 240     | 280    | 320    | 360 | 400 | 440 | 480 |

|---------------|------|------|---|----|--------|-----|------|--------|---------|--------|--------|-----|-----|-----|-----|

| DataPort      | 0000 | 0000 |   |    |        |     | 0000 | 000000 | 0001101 | 011000 | 000001 | 010 |     |     |     |

| - DataPort[0] | 0    | 0    |   |    |        |     |      |        |         |        |        |     |     |     |     |

| - DataPort[1] | 1    | 1    |   |    |        |     |      |        |         |        |        |     |     |     |     |

| -DataPort[2]  | 0    | 0    |   |    |        |     |      |        |         |        |        |     |     |     |     |

| DataPort[3]   | 1    | 1    | - |    |        |     |      |        |         |        |        |     |     |     |     |

Figure 3: Xilinx Chip scope result of RRC filter

The RRC filter design has been implemented on XCS3S400 field-programmable gate array (FPGA) device using Xilinx ISE 14.5i EDA tool. Comparison has been done with 16- bit input and coefficients of 8-bit, 12-bit, and 16-bits of word length. Table 1: shows the tradeoff of area and delay product for a fair comparison.

| <b>Table 1:</b> Comparison results of FIR filter in different |

|---------------------------------------------------------------|

| . 1                                                           |

|       |                                            | t     | echniq | ues    |                               |       |       |  |

|-------|--------------------------------------------|-------|--------|--------|-------------------------------|-------|-------|--|

| W     | ord length                                 | 8-bit | 12-bit | 16-bit | Area*delay<br>Improvement (%) |       |       |  |

|       | -                                          |       |        |        | 8bit                          | 12bit | 16bit |  |

| GC    | Proposed                                   | 167   | 281    | 345    | 23%                           | 39%   | 49%   |  |

| Delay | 2-bit BCSE                                 | 13.49 | 16.34  | 18.27  |                               |       |       |  |

| (ns)  | method                                     |       |        |        |                               |       |       |  |

| GC    |                                            | 2,878 | 3,532  | 3,771  |                               |       |       |  |

| Delay | Constant shift<br>multiplication<br>method | 285   | 33.33  | 41.6   | 62%                           | 62%   | 63%   |  |

The Table I shows the overall performance of the proposed design are 8%, 19%, 27% better than Xilinx multiplier core's performance and 62%,62%, and 63% better than 3-bit BCSE FIR filter architecture.

The synthesis results comparison of proposed architecture and Presented techniques in references shows in Table II. The synthesis result shows that the proposed technique has improvement in the LUT consumption, Gate Count and in speeds as compared with 3-bit BCSE method. The power estimation of RRC filter was 0.60W. In this Method RRC filter used less number of adders i.e. 6.

| Table | 2: | Synthesis | results | comparision |

|-------|----|-----------|---------|-------------|

|       |    |           |         |             |

|            |          | <b>ne</b> Sj | inche ono re | cours comp | anision |       |

|------------|----------|--------------|--------------|------------|---------|-------|

| References |          | Method       | Filter       | Max.       | Slices  | Gate  |

|            |          | used         | length       | freq.(MHz) | (LUTs)  | Count |

|            |          |              |              |            |         |       |

| sec        | Xc3s500e | 2-bit        | 49 taps      | 73.54M     | 160     | 153   |

| Propos     | Xc3s4000 | BCSE         | 16*17        | 66.4       | 249     | 232   |

| Prc        | Xc3s400a |              |              | 74.86      | 255     | 227   |

sr.ne

2319

| Xcs3000 | 3-bit | 20 taps | 64 | 1,601 | 23,878 |

|---------|-------|---------|----|-------|--------|

|         | BCSE  | 16*17   |    |       |        |

The proposed design of 2-bit BCSE-based FIR filter consumes less power and high operating speed than earlier work reported on 3-bit BCSE based filter design.

#### 5. Conclusion

This paper presents various problems occurred in designing the filter used in multistandard DUC, this is main component of SDR system. This offers the solutions to the problems and to make the filter is more efficient by reducing area and power with improvement in operating frequency. The proposed architecture is implemented on FPGA platform to validate the simulation results. This design can be enhanced with further reduction in area and power with better technique than BCSE-base design.

## 6. Acknowledgment

I am grateful to Mr. Yashwanth. N, Assistant Professor, Rajeev Institute of Technology, Hassan, for his constant guidance in completing the paper.

## References

- [1] J. Mitola, "The software radio architecture," IEEE Commun. Mag., vol. 33, no. 5, pp. 26–38, May 1995.

- [2] SDR Forum [Online]. Available: http://www.wirelessinnovation.org/ what\_is\_SDR

- [3] S. Im, W. Lee, C. Kim, Y. Shin, S. H. Lee, and J. Chung, "Implementation of SDR-eared digital IF channelized dechannelizer for multiple CDMA signals," IEICE Trans. Commun., vol. E83-B, no. 6, pp. 1282– 1289, Jun. 2000.

- [4] S.-F. Lin, S.-C. Huang, F.-S. Yang, C.-W. Ku, and L.-G. Chen, "Power-efficient FIR filter architecture design for wireless embedded system," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 51, no. 1, pp. 21–25, Jan. 2004.

- [5] Y. Son, K. Ryoo, and Y. Kim, "1:4 interpolation FIR filter," IEEE Electron. Lett., vol. 40, no. 25, pp. 1570– 1572, Dec. 2004.

- [6] P. K. Meher, S. Chandrasekaran, and A. Amira, "FPGA realization of FIR filters by efficient and flexible systolization using distributed arithmetic," IEEE Trans. Signal Process., vol. 56, no. 7, pp. 3009–3017, Jul. 2008.

- [7] K.-H. Chen and T.-D. Chieueh, "A low-power digitbased reconfigurable FIR filter," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 8, pp. 617–621, Aug. 2006.

- [8] O. Gustafsson, "Lower bounds for constant multiplication problems,"IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 11, pp. 974–978,Nov. 2007.

- [9] D. Shi and Y. J. Yu, "Design of linear phase FIR filters with high probability of achieving minimum number of adders," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 58, no. 1, pp. 126–136, Jan. 2011.