# Development of Wireless RGB LED PWM Controller on Low Cost CPLD

## Kamal Kant Sharma<sup>1</sup>, Vipin Kumar Gupta<sup>2</sup>

<sup>1</sup>M.Tech, Suresh Gyan Vihar University, Jaipur, India

<sup>2</sup>Assistant professor, Suresh Gyan Vihar University, Jaipur, India

Abstract: This article aims at development of Wireless RGB LED based on PWM controller by means of low cost CPLD. As the proficiency & light output of LEDs continues to obtain superior, application for color and white high brightness LEDs are apply enthusiastic on totally innovative markets. Power utilization and low charge are the major solution factors for making any electronic device. PWM organizer is used to control the quantity of power delivered to separate major color LED's. The incorporation of complete logic hooked on solitary chip CPLD satisfies the low cost issue. The absolute scheme reduces the dimension of the chip. These wireless RGB LED controller contain integer of separate mechanism are worn so these are very luxurious and multifaceted. Usually microcontrollers are worn for RGB LED regulator but we will use single CPLD chip for wireless RGB LED PWM controller and we will use a single CPLD chip for the entire peripherals. This panel can be used for all supplementary devices having similar pin out pattern. This pattern contains various peripherals, such as DIP Switches, Push Button Switches, LEDs, 7-Segment LED Displays, etc. We have used VHDL programming for creation CPLD device for the reason that it can be without difficulty ported to any mechanism so as to make likely mass invention. The board is by default programmed with a \*jam file, which contains CPLD board investigative System. This arrangement can be worn to examination all the peripherals that are on slat with CPLD, such as, DIP Switches, Push Button Switches, LEDs, 7-Segment Displays, headers, etc. Our machine features reconfigurable intend payable to reprogrammable reason.

Keywords: CPLD, Low cost, LED

### 1. Introduction

This purpose explains aspects of the assumption and put into practice of creating color-consistent, LED-based illumination yield .LEDs, as with all artificial products, have fabric and process variations that give way goods with matching dissimilarity in presentation. LEDs are binned and packaged to equilibrium the environment of the manufacturing process with the requests of the illumination manufacturing. Illumination-class LEDs are ambitious by application requirements and industry standards, including color steadiness and color and lumen preservation. Immediately as conventional lamps are sold by intensity (typically indicated by wattage) and color (warm or cool white), LEDs are binned for brightness (luminous flux) and color parameters (chromaticity).

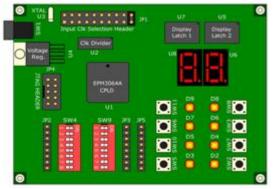

Figure 1.1: General Diagram of the CPLD Board

# 2. Application Design

The CPLD timber (Entry Level Tool) is deliberate intended for the MAX Device (EPM3064). This board can be worn intended for any other device having comparable pin out pattern. The client is confident to make sure out the panel schematics for the more details. This board contains a variety of peripherals, such as DIP Switches, Push Button Switches, LEDs, 7-Segment LED Displays, etc. interfaced with the MAX Device.

The slat is by defaulting automatic with a \*.jam file, which contains CPLD Board indicative System. This system can be used to test all the peripherals that are on board with the CPLD, such as, DIP Switches, Push Button Switches, LEDs, 7Segment LED Displays, headers, etc.

The second segment gives the in order about all the hardware mechanism and peripherals on this CPLD Board. The third segment gives the in sequence concerning the CPLD Board Diagnostic System that is surrounded within the CPLD. This segment gives facts concerning all the tests that can be done using this system and how to use this system for testing involved peripherals.

The fourth segment gives indication mapping flanked by the CPLD and all the peripherals.

The fifth segment indicates the position objects connected with this slat.

This section gives the component details about the CPLD Board Hardware. This section describes all the peripherals that are integrated with the CPLD.

The comprehensive figure of the CPLD Board is shown. As exposed in the figure, the board contains two 8-way DIP Switches, eight Push Button Switches, eight LEDs, two 7-Segment LED Displays, Connection headers for inputs and outputs (shared), JTAG header for downloading the bit files and ten clock selection options for the CPLD system clock. The consequent parts describe the Hardware components that are incorporated with the CPLD.

#### 2.1 Hardware Mechanism MAX CPLD

This board is mainly designed around EPM3064ALC44-10 (U1) (MAX CPLD). The CPLD used is a 44-pin PLCC package used in PLCC socket. So the user can change the CPLD part if it gets damaged. This also gives the flexibility to the user to replace the EPM3064 part with another CPLD part having similar pin out configuration to be used with the appropriate HDL design file.

The core voltage required for the CPLD is 3.3 volts while the IOs can be operated at 3.3 volts or 5.0 volts. This board uses 3.3 volts as both the core voltage and IO voltage. Since the IOs are 5.0 volt tolerant, user can use 3.3 volt or 5.0 volt input to the CPLD.

#### **Power Supply Jack**

The CPLD board has an input power supply jack (SW1) to get the unregulated supply to the input of the regulator of +3.3V. The polarity of the Jack is center Positive. The user can use 6VDC, 500mA SMPS power supply with this board.

#### **Clock Selection Header**

This board contains a 20-pin Clock Selection Header (JP1) for selecting the input system clock to the CPLD. The board uses 32.768 KHz Crystal to generate its clock. This 32.768 KHz frequency is divided by 14-Stage ripple-carry Binary Counter/Divider and Oscillator chip HEF4060. This chip gives 10 clock outputs, out of which user can select any clock (as per the requirement) using Clock Selection Header (JP1).

#### JTAG Download Header

This board contains the standard JTAG download header (JP4) to download the design into the CPLD (\*.jam files, \*.jbc files, etc.). This header can also be used for the JTAG Boundary Scan Testing of the CPLD (if the JTAG pins are not used as IOs in the design). The user can use Altera's Byte Blaster or Master Blaster or USB Blaster cable to download the design into the CPLD using this header.

This board contains the standard JTAG download header (JP4) to download the design into the CPLD (\*.jam files, \*.jbc files, etc.). This header can also be used for the JTAG Boundary Scan Testing of the CPLD (if the JTAG pins are not used as IOs in the design). The user can use Altera's Byte Blaster or Master Blaster or USBBlaster cable to download the design into the CPLD using this header.

#### 8-Way DIP Switches

The CPLD Board contains two 8-way DIP switches (SW4 & SW9), which can be used as two 8-bit user inputs. The CPLD reads HIGH when the DIP switch is turned OFF and reads LOW when the DIP switch is turned ON.

#### Push Button Switches

This board contains eight push button switches (SW2-SW11 except SW4 & SW9), which can be used as user inputs. The CPLD reads LOW when the Push Button Switch is pressed and reads HIGH when the Push Button Switch is released.

All the Push Button Switches (and hence LEDs) are also mapped one-to-one with all the pins of 8-pin header JP5. This facility is provided to give the flexibility to use this 8pin header as either external input or external output or the combination of both. The user can keep all the Push Button switches released and give external inputs to JP5 to use them as external inputs to the CPLD. When used in the output mode, whatever data is coming out on the LEDs is straight away available on the corresponding pins of the JP5 header.

#### LED

This board contains eight Light Emitting Diodes (LEDs) (D2-D9), which can be used as user outputs. The CPLD outputs LOW to turn ON the LEDs and outputs HIGH to turn OFF the LEDs

#### 8 - System Level Solutions

All the LEDs (and hence Push Button Switches) are also mapped one-to-one with all the pins of 8-pin header JP5. This facility is provided to give the flexibility to use this 8pin header as either external input or external output or the combination of both. The user can keep all the Push Button switches released and give external inputs to JP5 to use them as external inputs to the CPLD. When used in the output mode, whatever data is coming out on the LEDs is straight away available on the corresponding pins of the JP5 header.

#### 7-Segment LED Display

This board contains two 7-segments LED displays (U6 & U8), which can be used as user outputs. The CPLD board has common anode 7-segment LED displays on the board hence the CPLD should output LOW to turn ON a particular segment and output HIGH to turn OFF a particular segment.

The board design is such that a 7-bit data bus (for Segments A-G) is shared between the two 7-segment LED displays through separate transparent latches 74HC573 (U5 & U7) for each of the displays (U6 & U8 respectively). The latches have active high Latch Enable signals. Hence the user should give a positive pulse to latch the 7-bit display data corresponding to the segments A-G for the respective 7-segment LED displays.

Figure 1.2: LED Display

# 3. Working & Hardware Configuration

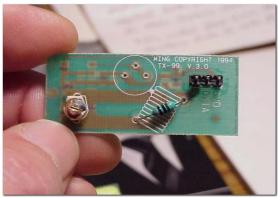

The grown-up schematics were scanned and appealing reduced quality. These new ones be supposed to make it significantly easier to be familiar with the parts used for the development. The Ming RF transmitter and receiver boards used for this development are moderately economical and carry out worthily allowing for the inadequate price. Using the quarter wave antennas, we have had some outstanding consequences with working remoteness as well as largely function. The Ming modules come prepared to plug up into your application and only require these simple interface circuits shown here to construct your own complete RF distant manage organization. This development uses the Ming TX-99 V3.0 300 MHz AM, RF Transmitter module exposed under for transmitting data.

Figure1.3: Ming TX-99 V3.0

The picture above shows the Ming TX-99 V3.0. Once you have the Ming board you're prepared to construct the interface circuit exposed underneath. The switches SW1-SW4 allow you choose the logic levels or (data) to drive to the recipient. The logic levels present at the Holtek HT-12E encoder pins D0-D3 will be transferred to the recipient. The circuit exposed below will broadcast constantly if the pin #14 (TE) is left linked to earth. If you wish for your transmitter to transmit only when you push a button, simply break the circuit ground connection using another switch. By via another switch to split the earth association, you will hoard power in your transmitter circuit and only transmit when you push the pushbutton exchange that you're via to split the earth power association.

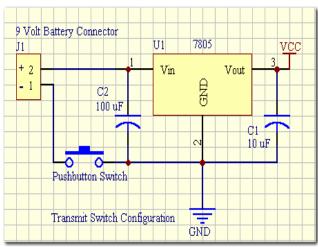

Figure 1.4 Transmit Switch Configuration

Using the pushbutton switch to make/break the ground connection for the power circuit to your transmitter, you save power and only transmit data when you push the switch. You can use a standard LM7805 +5 volt regulator, or the smaller version using a 78L05 +5 volt regulator in the T0-92 style package to save space. The 78L05 T0-92 style +5 volt regulators is about the same size as a normal transistor and allows you to build the transmitter circuit small enough to fit into a small handheld plastic enclosure. The power supplies for this route are negligible and the 78L05 is more than able of delivering enough current for process.

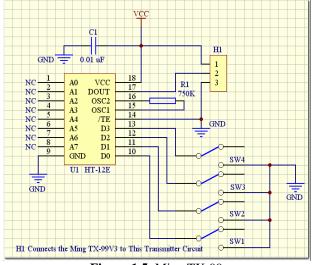

The header marked H1 in the schematic below allows you to simply plug the Ming transmitter module directly into the transmitter circuit. The DOUT pin #17 of the HT-12D sends serial data to the Ming TX-99 module which in turn transmits this serial data to the receiver circuit shown in the receiver schematic later on in this project article.

Figure 1.5: Ming TX-99

Below is a picture of the Ming RE-99 V3.0A RF Receiver used to receive data transmitted by The TX-99 shown at the above.

Figure 1.6: Ming RE-99 V3.0A

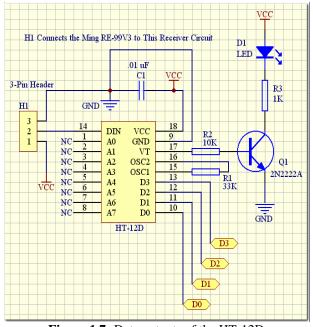

Once you have the Ming RE-99 V3.0 shown above, you're prepared to construct the interface circuit shown below. The 3-pin header lets you simply plug the Ming RE-99 receiver board into your receiver circuit shown below. The data outputs of the HT-12D shown below will correspond directly to the logic levels present on the transmitter circuit shown with the HT-12E above. Pin #17 (VT) on the HT-12D is the valid transmit pin. Once a valid transmission has been received from the transmitter, this pin will go to a logic (1) or high turning the transistor and LED on.

Data received from the transmitter section will then be latched on the output pins of the HT-12D. The data outputs of the HT-12D will remain "latched" or in the last valid logic states until another valid reception is received requesting a change of state on the logic outputs.

Figure 1.7: Data outputs of the HT-12D

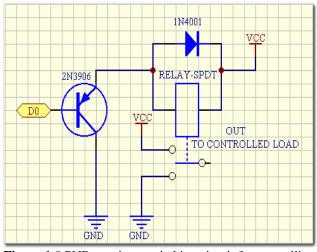

The receiver circuit can control solid state relays or mechanical types. Below is the circuit we use for controlling solid state relays directly from the outputs of the HT-12D circuit shown above. The diodes were added as fly back protection should I ever need to replace one of the solid state relays with a mechanical type. If your application calls for solid state relays only, just eliminate the diodes altogether. Check the data sheet for the relays you intend to use for added safety. When in doubt, use the diodes anyway. Better safe than sorry and diodes are the cheapest part of this circuit anyway.

To attach the driver circuit below, simply connect D0 to the same output of the HT-12D circuit shown in the receiver schematic above. Attach the base of the PNP transistor directly to the data out pin D0 on the HT-12D. VCC will always be present across the relay coil, but ground will be switched by the PNP transistors. When the transistor is off, so is your relay. A logic (0) or ground at the base of the PNP transistor will forward bias the transistor and energize your relay. Effortless and easy, yet very useful and within the budget of most hobbyists.

Figure 1.8 PNP transistor switching circuit for controlling solid state or mechanical relays

Construct four of the switching circuits shown above if we want to use all four of the control outputs from the HT-12D. Get note if we use a solid state transmit with this circuit, we may require to comprise a series present preventive resistor from the emitter side of the PNP transistor to keep away from overdriving the LED inside the solid state relay.

Using the Ming pre-made RF modules makes building an RF Transmitter & Receiver pretty easy. The Holtek HT-12E and HT-12D Encoder/Decoder IC's handle the data encoding & decoding. With the Ming transmitter & receiver modules, you only need to build the interface circuitry shown here to have a complete RF remote control system.

#### **3.1 Circuit Operation**

The Holtek HT-12E IC encodes 12-bits of information and serially transmits this data on receipt of a Transmit Enable, or a LOW signal on pin-14 /TE. Pin-17 the D\_OUT pin of the HT-12E serially transmits whatever data is available on pins 10, 11, 12 and 13, or D0,D1,D2 and D3. Data is transmitted at a frequency selected by the external oscillator resistor. See the encoder/decoder datasheets for details.

By using the switches attached to the data pins on the HT-12E, as shown in the schematic, we can select the information in binary format to send to the receiver. The receiver section consists of the Ming RE-99 and the HT-12D decoder IC. The DATA\_IN pin-14 of the HT-12D reads the

12-bit binary information sent by the HT-12E and then places this data on its output pins. Pins 10,11,12 and 13 are the data out pins of the HT-12D, D0,D1,D2 and D3.

The HT-12D receives the 12-bit word and interprets the first 8-bits as address and the last 4-bits as data. Pins 1-8 of the HT-12E are the address pins. Using the address pins of the HT-12E, we can select different addresses for up to 256 receivers. The address is determined by setting pins 1-8 on the HT-12E to ground, or just leaving them open. The address selected on the HT-12E circuit must match the address selected on the HT-12D circuit (exactly), or the information will be ignored by the receiving circuit.

When the received addresses from the encoder matches the decoders, the Valid Transmission pin-17 of the HT-12D will go HIGH to indicate that a valid transmission has been received and the 4-bits of data are latched to the data output pins, 10-13. The transistor circuit shown in the schematic will use the VT, or valid transmission pin to light the LED. When the VT pin goes HIGH it turns on the 2N2222 transistor which in turn delivers power to the LED providing a visual indication of a valid transmission reception.

#### 3.2 Scheming the Project by a Microcontroller

Using these RF transmitter & receiver circuits with a Microcontroller would be simple. We can simply replace the switches used for selecting data on the HT-12E with the output pins of the microcontroller. Also we can use another output pin to select TE, or transmit enable on the HT-12E. By taking pin-14 LOW we cause the transmitter section to transmit the data on pins 10-13.

To receive information simply hook up the HT-12D output pins to the microcontroller. The VT, or valid transmission pin of the HT-12D could signal the microcontroller to grab the 4-bits of data from the data output pins. If you are using a microcontroller with interrupt capabilities, use the VT pin to cause a jump to an interrupt vector and process the received data.

The HT-12D data output pins will LATCH and remain in this state until another valid transmission is received.

We will need a few pieces of 22 gauge wire for the antennas on the RE-99 and TX-99. Both units come with full instructions for selecting the length of wire to use for each antenna. For a quarter wave antenna you will need 9.36 inches of 22 gauge wire for both the transmitter and receiver boards.

#### 3.3 Range of Operation

The standard working range using (only) the LOOP TRACE ANTENNA on the transmitter board is about 50 feet. By linking a quarter wave antenna using 9.36 inches of 22 gauge wire to both circuits, we can expand this range to numerous hundred feet. Your genuine range may vary due to your completed circuit design and environmental circumstances.

The transistors and diodes can be substituted with any frequent corresponding variety. These will usually depend

on the types and capacities of the particular loads you want to manage and should be chosen consequently for your projected relevance.

# 4. Conclusion

The objective of this technological investigate is to enlarge the essential level of considerate in the middle of the variety of members of the illumination area about the possibilities of control as well as potential applications for those technologies. This article aims at development of Wireless RGB LED based on PWM controller by means of low cost CPLD. As the proficiency & light output of LEDs continues to obtain superior, application for color and white high brightness LEDs are apply enthusiastic on totally innovative markets. Power utilization and low charge are the major solution factors for making any electronic device. PWM organizer is used to control the quantity of power delivered to separate major color LED's. The incorporation of complete logic hooked on solitary chip CPLD satisfies the low cost issue. The absolute scheme reduces the dimension of the chip. These wireless RGB LED controller contain integer of separate mechanism are worn so these are very luxurious and multifaceted. Usually microcontrollers are worn for RGB LED regulator but we will use single CPLD chip for wireless RGB LED PWM controller and we will use a single CPLD chip for the entire peripherals. This panel can be used for all supplementary devices having similar pin out pattern. This pattern contains various peripherals, such as DIP Switches, Push Button Switches, LEDs, 7-Segment LED Displays, etc. We have used VHDL programming for creation CPLD device for the reason that it can be without difficulty ported to any mechanism so as to make likely mass invention. The board is by default programmed with a \*.jam file, which contains CPLD board investigative System. This arrangement can be worn to examination all the peripherals that are on slat with CPLD, such as, DIP Switches, Push Button Switches, LEDs, 7-Segment Displays, headers, etc. Our machine features reconfigurable intend payable to reprogrammable reason.

# References

- [1] J. Abu-Qahouq, H. Mao, and I. Batarseh. Multiphase voltage-mode hysteretic controlled DC–DC converter with novel current sharing. IEEE Trans. Power Electron.,19(6):1397–1407, November 2004.

- J. A. Abu-Qahouq, H. Mao, H. J. Al-Atrash, and I. Batarseh. Maximum efficiencypointtracking(MEPT)methodanddeadtimecont rol. InProc. IEEE Power Electron.Spec. Conf., volume 5, pages 3700–3706, 2004.

- [3] B. Acker, C. R. Sullivan, and S. R. Sanders. Synchronous rectification with adaptive timing control. In Proc. IEEE Power Electron. Spec. Conf., volume 1, pages 88–95,1995.

- [4] B. Arbetter and D. Maksimovi'c. Control method for low-voltage DC power supplyin battery-powered systems with power management. In Proc. IEEE Power Electron.Spec. Conf., volume 2, pages 1198–1204, 1997.

- [5] K. B. Ariyur and M. Krsti'c. Analysis and design of multivariable extremum seeking. In Proc. American Control Conf., pages 2903–2908, May 2002.

- [6] S. Ashley. Power-thrifty PCs. Scientific American, 290(6):31–32, June 2004.132

- [7] K. J. <sup>°</sup>Astro<sup>°</sup>mandT.H<sup>°</sup>agglund. PID Controllers: Theory, Design, and Tuning. Instr.Soc. of America, Research Triangle Park, North Carolina, second edition, 1995.

- [8] K. J. <sup>°</sup>Astro<sup>°</sup>mandB.Wittenmark. Adaptive Control. Addison Wesley Longman, second edition, 1995.

- [9] S.BanerjeeandG.C.Verghese(Editors). Nonlinear Phenomena in Power Electronics:Attractors, Bifurcations, Chaos, and Nonlinear Control. NewYork: IEEEPress, 2001.

- [10] A. Barrado, R. Va'zquez, E. Ol'ıas, A. La'zaro, and J. Pleite. Theoretical study and implementation of a fast transient response power supply. IEEE Trans. Power Electron.,19(4):1003–1009, July 2004.

- [11] D. P. Bertsekas. Nonlinear Programming. Belmont, MA: Athena Scientific, secondedition, 1999.

- [12] T. D. Burd, T. A. Pering, A. J. Stratakos, and R. W. Brodersen. A dynamic voltagescaled microprocessor system. IEEE JSSC, 35(11):1571–1580, November 2000.

- [13] C. Calwell and A. Mansoor. AC-DC server power supplies: Making the leap to higher efficiency. In IEEE Appl. Power Electron. Conf., pages 155–158, 2005.

- [14] S. Canter and R. Lenk. Stabilized power converter having quantized duty cycle.United States Patent Number 5,594,324, January 1997.

- [15] B. Carroll. Cost-effective digital control for core power. In Darnell Digital PowerForum, volume CD-ROM, September 2004.133

- [16] A. P. Chandrakasan and R. W. Brodersen. Low Power Digital CMOS Design. Boston, MA: Kluwer Academic Publishers, 1995.

- [17] G. Chinn, S. Desai, E. DiStefano, K. Ravichandran, and S. Thakkar. Mobile PCplatforms enabled with Intel CentrinoTM mobile technology. Intel Tech. J., 7(2), May2003.

- [18] W. D. Collins. Digital technology invades power supply control market (power management components topical report). [Online]. Available: http://www.isuppli.com,2003.

- [19] Intel Corp. Voltage Regulator–Down (VRD) 10.1.

[Online].

Available:http://developer.intel.com/design/Pentium4/d ocumentation.htm, July 2004.

- [20] Intel Corp. Moore's Law. [Online]. Available:http://www.intel.com/research/silicon/moores law.htm, 2005.

- [21] International Rectifier Corp. IR3081: XPHASETM VR 10.0 control IC. Data Sheet, September 2003.

- [22] A. P. Dancy, R. Amirtharajah, and A. P. Chandrakasan. High-efficiency multipleoutput DC-DC conversion for low-voltage systems. IEEE Trans. VLSI Sys., 8(3):252– 263, June 2000.