# Carbon Nanotubes Field Effect Transistor: A Review

### Shaifali Ruhil<sup>1</sup>, Jyoti Sehgal<sup>2</sup>, Komal Rohilla<sup>3</sup>

<sup>1</sup>Vaish College of Engineering, M.D.U, Rohtak, Haryana, India

<sup>2</sup>AP in Vaish College of Engineering, M.D.U, Rohtak, Haryana, India

<sup>3</sup>Vaish College of Engineering, M.D.U, Rohtak, Haryana, India

Abstract: In this paper we have focused on the carbon nano tube field effect transistor technology. The advantages of CNTFET over MOS technology are also discussed. The structure and types of CNTFET are given in detail along with the variation of threshold voltage with respect to the alteration in CNT diameter. The characteristics curve between gate to source current and drain to source voltage is plotted. Various fixed and variable parameters of CNT are also focused.

Keywords: CNTFET, Nano tube diameter, 3-D structure, MOSFET, I-V characteristics, fixed and variable parameters

### 1. Introduction

Paper ID: SUB152631

According to Moore's law, the numbers of transistors on an IC are increasing. This increased number of transistors results in the demand for decreasing the size of transistor and so the circuit size is also reduced. This gives birth to nanoscale technology. CMOS has flexible nature but still it faces many challenges in the field of nanotechnology. As the CMOS is scaled down then the power dissipation of the device is increased to a great extent. The leakage current also increases simultaneously. Short channel effect is another destructive challenge of MOSFET device. CNTFET has been announced as one of the most popular replacement for conventional MOSFET due to its similarities in terms of manufacturing process and electrical properties. In it the flow of electrons follow the ballistic transport.[1] Also the leakage current is very low. Thus CNTFET exhibits excellent performance characteristics over conventional MOSFET.

Figure 1: Graphine sheet forming CNT [2]

### 2. CNTFET Review

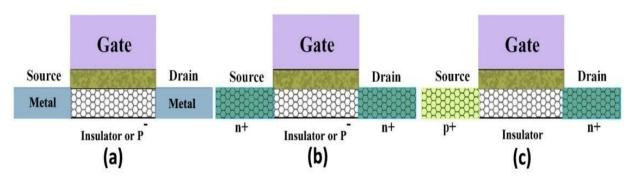

The important characteristic of CNTFET is its flexible behavior of changing the threshold voltage ( $V_{th}$ ) by adopting different values of diameter for CNTs. [3] CNTFET is of 3 types: 1) Schottky Barrier CNFET (SB-CNFET): In this type the drain and source are directly connected to the channel.[4]. 2) MOSFET type CNFET (MOS-CNFET): In it the connecting source and drain of the impurities has been formed. 3) Tunneling CNFET (T-CNFET): This CNFET has an excellent cut-off characteristic. [7]. The structures of 3 types of transistors are shown in figure 2.

Figure 2: SB-CNFET (b) MOS-CNFET (c) T-CNFET [8]

Volume 4 Issue 3, March 2015

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

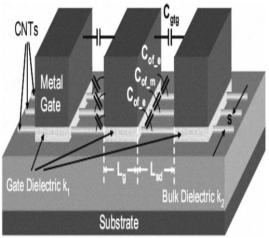

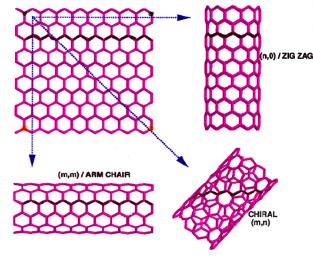

The Leakage power is negligible when CNTFET is in turn off state. [9]. The structural and electrical characteristics are similar to MOSFETs, which facilitates the reuse of previous MOSFET based architectures and fabrication processes [10]. The structure of a MOSFET-like CNTFET is given in Fig 3. The main point of contrast is that in the CNTFET, the current flows through CNTs instead of the flow of holes and electrons through the physical channel in the substrate. The CNTs under the gate region are intrinsic to have semiconducting behavior and can be controlled by the input voltage of gate [11]. The fabrication of single-wall CNT (SWCNT) transistors came into existence in [9], [12]. A SWCNT is consists of a single hollow tube of rolled graphene sheet. This can either be metallic in nature or semiconducting in nature, depending on the values of vectors m and n.[13],[10],[14] This is possible only because of the angle of atoms arranged along the nanotube. This angle is represented by a 2-D vector known as the chirality vector .As shown in fig 4, CNTs can be rolled in 3 different ways, namely Armchair, chiral and Zigzag.[15].

Figure 3: 3-D structure of CNTFET[16]

#### STRIP OF A GRAPHENE SHEET ROLLED INTO A TUBE

Figure 4: Types of CNTFET according to chirality

Paper ID: SUB152631

# Diameter Behaviour Rest of [(n-m)/3] = 0 $\longrightarrow$ Metallic Rest of $[(n-m)/3] \neq 0$ $\longrightarrow$ Semiconducting

Now the value of threshold voltage (Vth) [17] according to diameter D is given below:

$$Vth = 0.43 \div Dcnt(nm) \tag{1}$$

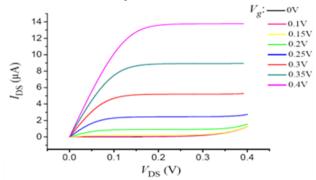

Based on the above observation, for different values of D we calculated different values of vth. The curve between I<sub>DS</sub> and  $V_{DS}$  is shown below in figure 5:

**Figure 5:** Plot b\w I-V [18]

The CNTFET has 2 types of parameters: fixed parameters and variable parameters. These are given below in tabular manner.

**Table 1:** Parameters specifications

| Fixed Parameters         |       | Variable Parameters     |           |

|--------------------------|-------|-------------------------|-----------|

| Power supply             | 0.9 V | No. of CNTs per device  | Nominal:8 |

| Oxide thickness          | 4nm   |                         |           |

| Gate\source\drain length | 16nm  | CNT diameter            | 1-6nm     |

| Width of metal gate      | 36nm  |                         |           |

| CNT pitch                | 4nm   | Metallic CNT proportion | 0-33%     |

### 3. CNTFET- Based Logic Circuits

Earlier CNTFET was only used for resistive load circuits. As the time passed, the advancements in CNTFET were also done. Later on it was used for logic gates like inverter, AND gate, NAND gate, NOR gate etc. It is also used in the designing of SRAM cells. A new logic called ternary logic is also developed. Ternary logic functions are used when a third significant value other than binary value is introduced. The ternary values to represent true, undefined and false states are 2, 1, and 0 respectively. The main advantage of it is that it reduces the number of computational steps required. It is also used for full adder and multipliers when the conventional binary logic gate design is combined with the ternary logic design.[19]. To evaluate the performance of a CNTFET, various simulation models have been proposed. The CNFET HSPICE model is widely used in circuit design and simulation. The window of HSPICE TOOL version B 2008.09 is shown below.

## International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438

Figure 6: HSPICE tool window

### 4. Conclusion

This paper provides the summary of different types of CNTFETs and their structures. The spectacular conclusion is that the threshold voltage varies according to the diameter of CNT. 4-12 CNTs could be used according to the requirement. CNTFET proves to be an efficient device for nano electronics in future.

### References

- [1] SeyyedAshkanEbrahimi,PeimanKeshavarzian,SaeidSoro uri,Mahyar Shahsavari, low power CNTFET based ternary full adder cell for nano electronics, International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307, Volume-2, Issue-2, May 2012.

- [2] Djamil RECHEM and Saida LATRECHE, Nanotube Diameter Effect on the CNTFET Performances, 5th International Conference: Sciences of Electronic, Technologies of Information and Telecommunications March 22-26, 2009 TUNISIA.

- [3] Aliakbar Rezaei, Mehdi Masoudi, Fazel Sharifi, Keivan Navi, A Novel High Speed Full Adder Cell based on Carbon Nanotube FET (CNFET), Int. J. Emerg. Sci.(IJES), issue 4(2),pp. 64-74, June 2014.

- [4] S. Lin, Y.-B. Kim, and F. Lombardi, "A novel CNTFET-based ternary logic gate design," in Circuits and Systems, 2009. MWSCAS'09. 52nd IEEE International Midwest Symposium on, 2009, pp. 435-438.

- [5] A. Raychowdhury and K. Roy, "Carbon nanotube electronics: design of high-performance and low-power digital circuits," Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 54, pp. 2391-2401, 2007.

- [6] Y. B. Kim, Y.-B. Kim, and F. Lombardi, "A novel design methodology to optimize the speed and power of the CNTFET circuits," in Circuits and Systems, 2009. MWSCAS'09. 52nd IEEE International Midwest Symposium on, 2009, pp. 1130-1133.

- [7] Ronak Zarhoun, Mohammad Hossein Moaiyeri, Samira Shirinabadi Farahani, and Keivan Navi, An Efficient 5-Input Exclusive-OR Circuit Based on Carbon Nanotube FETs, ETRI Journal, Volume 36, Number 1, February 2014.

Paper ID: SUB152631

- [8] Aliakbar Rezaei, Mehdi Masoudi, Fazel Sharifi, Keivan Navi, A Novel High Speed Full Adder Cell based on Carbon Nanotube FET (CNFET), Int. J. Emerg. Sci.(IJES), issue 4(2),pp. 64-74, June 2014.

- [9] S. Lin et al., "A New SRAM Cell Design Using CNTFETs," Int. SoC Design Conf., vol. 1, Busan, South Korea, Nov. 24-25, 2008,

- [10] M.H. Moaiyeri, K. Navi, and O. Hashemipour, "Design and Evaluation of CNFET-Based Quaternary Circuits," Circuits, Syst., Signal Process., vol. 31, no. 5, Oct. 2012, pp. 1631-1652.

- [11] A. Lin et al., "Threshold Voltage and On-Off Ratio Tuning for Multiple-Tube Carbon Nanotube FETs," IEEE Trans. Nanotechnol., vol. 8, no. 1, Jan. 2009, pp.4-9.

- [12] N. Patil et al., "Scalable Carbon Nanotube Computational and Storage Circuits Immune to Metallic and Mispositioned Carbon Nanotubes," IEEE Trans. Nanotechnol., vol. 10, no. 4, July 2011, pp.744-750.

- [13] A. Raychowdhury and K. Roy, "Carbon Nanotube Electronics: Design of High-Performance and Low-Power Digital Circuits," IEEE Trans. Circuits Syst I, Reg. Papers, vol. 54, no. 11, Nov. 2007, pp. 2391-2401

- [14] P. McEuen, M.S. Fuhrer, and H. Park, "Single-Walled Carbon Nanotube Electronics," IEEE Trans. Nanotechnol., vol. 1, no. 1, Mar. 2002, pp. 78-85.

- [15] J. Deng, Device Modeling and Circuit Performance Evaluation for Nanoscale Devices: Silicon Technology beyond 45 nm Node and Carbon Nanotube Field Effect Transistors, doctoral dissertation, Stanford University, 2007.

- [16] Hamed Shahidipour, Yue Zhong, Arash Ahmadi, Koushik Maharatna, "Effects of CNT Diameter Variability on a CNFET Based SRAM" 2010 Asia Pacific Conference on Circuits and Systems (APCCAS 2010) 6 9 December 2010, Kuala Lumpur, Malaysia.

- [17] Sneh Lata Murotiya, Anu Gupta, Design and Analysis of CNTFET Based D Flip-Flop, International journal of electronics and communication engineering and technology (IJECET), Special Issue (November, 2013), pp. 144-149.

- [18] Rasmita Sahoo1, R. R. Mishra," Carbon Nanotube Field Effect Transistor: Basic Characterization and Effect of High Dielectric Material" International Journal of Recent Trends in Engineering, Vol 2, No. 7, November 2009.

- [19] Sanjeet Kumar Sinha, Saurabh Choudhury, "CNTFET based Logic Circuits: A Brief Review" International Journal of Emerging Technology and Advanced Engineering Website: www.ijetae.com (ISSN 2250-2459, Volume 2, Issue 4, April 2012).