# Design and Simulation of NOT and NAND Gate Using Hybrid SET-MOS Technology

# Daya Nand Gupta<sup>1</sup>, S. R. P. Sinha<sup>2</sup>

<sup>1</sup>Research scholar, Department of Electronics Engineering, Institute of Engineering and Technology, Lucknow, India

<sup>1</sup>Associate Professor, Department of Electronics Engineering, Institute of Engineering and Technology, Lucknow, India

**Abstract:** Single Electron Transistor (SET) is an advanced technology for future low power VLSI devices. SET has high integration density and a low power consumption device. While building logic circuits that comprise only of SETs, it is observed that the gate voltage at the input must be higher than the power supply of SET for better switching characteristics. This limitation of SET in the power and gate supply voltages makes it practically inappropriate to build circuits. An approach to overcome this problem, hybridization of SET and CMOS transistor is implemented. In this paper, different types of hybrid SET-MOS circuits are designed such as hybrid SET-MOS inverter and NAND gate is designed and implemented. All the circuits are verified by means of PSpice simulation software version 16.5.

Keywords: Single Electron Transistor (SET), Coulomb Blockade, Orthodox Theory, Hybrid SET-MOS, Pspice

## 1. Introduction

Due to continuous reduction of the physical dimensions of transistor towards the nanometer scale as per the trend of Moore's law, it is obvious that in the near future it would be impossible for further reduction due to quantum effects. The minimum feature size in an integrated circuit has reduced from >1  $\mu$ m in 1970 to ~ 20 nm in 2013, and it is expected that by 2021, it may be possible to define features smaller than ~ 10 nm (International Technology Roadmap for Semiconductors, 2013). The devices which exhibit charging effects including Coulomb blockade are referred to as single-electron devices. A SET circuit operating in the SET regime can have the smallest available transition time 10<sup>-15</sup> s, the lowest possible power consumption (working with just a few electrons at  $\mu V$  or mV voltage ranges) and it can have the highest achievable voltage gain. A SET circuit operating in the SET regime can even obtain a switching time in the order of 10<sup>-15</sup> s, while in CMOS technology the switching speeds are predicted to be on the order of 10<sup>-10</sup> s and is probably never able to compete to the switching speed values of SET technology.

#### 1.1 Theory of Single Electron Transistor

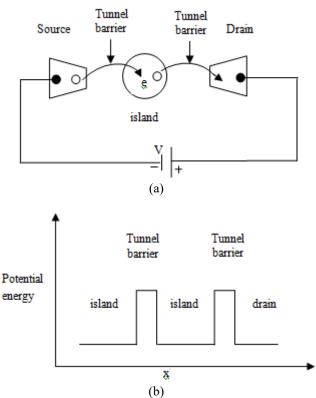

The principle of operation of SET devices is based on electron tunneling through a nanoscale junction (Fig. 1). The electrons tunnels through the channel one-by-one due to its particular architecture that includes two tunneling junctions [1], [2] and one conductive island [3]. If the charging energy associated with adding the electrons to the island is overcome then only electrons can tunnel onto the island [4].

# 1.1.1 Orthodox Theory

The 'Orthodox' theory of single-electron tunneling, describes an important charging effect such as Coulomb blockade and Coulomb oscillation [5]. Later this theory

revised by Likharev [6]. The orthodox theory makes the following approximations:

- 1) The quantization of electronic energy inside the conductors is ignored, i.e. the electron energy spectrum is treated as continuous.

- 2) Time for electron tunneling through the barrier is assumed to be negligibly small  $(T_t \sim 10^{-15} \text{ s})$  in comparison with other time scales (including the interval between neighboring tunneling events).

- 3) Cotunneling events are ignored. This assumption is valid if the resistance  $R_T$  of the tunnel barriers of the system is much higher than the quantum unit of resistance  $R_O$ .

$$R_T = R_Q, R_Q = \frac{h}{a^2} \approx 25.8 \, k\Omega \tag{1}$$

This assumption is valid only when the electrons are well localized in the island. However, in quantum mechanics it is uncertain. According to Heisenberg's energy uncertainty  $(\Delta E)$  principle,

$$\Delta E \Delta t > h \tag{2}$$

where h is plank's constant and  $\Delta t$  is the quantum uncertainity.

## 1.1.2 Coulomb Blockade Effects

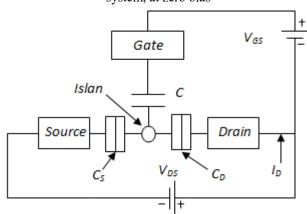

The Coulomb blockade or single-electron charging effect [4], [6], which allows for the precise control of small numbers of electrons, provides an alternative operating principle for nanometer-scale devices. In addition, the reduction in the number of electrons in a switching transition greatly reduces circuit power dissipation, raising the possibility of even higher levels of circuit integration. The SET uses this effect to control the charging of a small 'island' electrode by electrons one at a time [7]. Fig. 2 showed a basic SET, where an island electrode is isolated from source and drain electrodes by tunneling potential barriers with capacitance  $C_S$  and  $C_D$ . A gate electrode couples to the island electro statically via the gate capacitance  $C_G$  and  $C_G$  is used to modulate the generated current.

Figure 1: The single-island, double tunnel junction system (a) Schematic diagram, (b) The potential energy across the system, at zero bias

Figure 2: Circuit diagram of single-island double tunnel junction SET

The charging energy of the system is defined as:

$$E_C = \frac{e^2}{2C_{\Sigma}} \tag{3}$$

where e is the charge of an electron and  $C_{\Sigma}$  is the capacitance of this system ( $C_{\Sigma} = C_{S}+C_{D}+C_{G}$ ), associated with a single electron prevents sequential tunneling through the island below a threshold voltage,  $V_{th}$  which can be controlled by applying a voltage  $V_{g}$  to the gate. The threshold voltage,  $V_{th}$  is the minimum value required for tunneling as shown below [8]:

$$V_{th} = \frac{\bar{E}_C}{e} = \frac{e}{2C_{\Sigma}} \tag{4}$$

$E_C$  is the charging energy of the system. As long as the threshold voltage is not reached the junction is blocked.

In order to observe coulomb blockade effects, there are two necessary conditions. One condition is that the charging energy  $E_C$  of single excess electron on a quantum dot is much greater than the thermal energy [9], [10].

$$E_C = \frac{e^2}{2C_{\Sigma}} \gg k_B T \tag{5}$$

In the above expressions,  $k_B$  is Boltzmann's constant and T is the temperature of the system. From equation 5

$$T < \frac{E_C}{k_B} \tag{6}$$

Here, the Coulomb blockade is effective at this temperature. The other condition is that the tunneling resistance,  $R_T$  of the tunneling junction must be larger than quantum resistance [9].

$$R_T \gg R_Q = \frac{h}{r^2} \approx 25.8 \, k\Omega$$

(7)

where h is Planck's constant and  $R_{\rm Q}$  is the quantum resistance.

Based on the Coulomb blockade effects, many interesting devices are possible such as precise current standards, very sensitive electrometers, logic gates and memories with ultra low power consumption, down scalability to atomic dimensions, and high speed operation [8]. Therefore, these effects are experimentally verifiable only for very small high-resistance tunnel junctions, meaning small particles with small capacitances and at very low temperatures. Different modeling and simulation techniques Macro modeling of SET [11], Monte Carlo method [9], [12], [13] and SIMON [9] are used for efficient circuit simulation SET.

#### 1.2 Single-electron Transistor Logic

ŀ

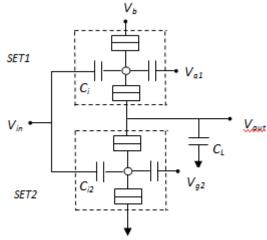

The circuit of the basic quasi-CMOS inverter is shown below in Fig. 3. The quasi-MOSFET surrounded by the dotted line is composed of two tunnel junctions and two conventional capacitors. In this quasi-MOSFET, the functions of quasi-n-MOSFET and quasi-p-MOSFET are switched by simply changing the second gate bias voltage. In the quasi-CMOS inverter, the output voltage is proportional to the charge stored in the capacitor  $C_L$  [14].

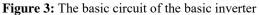

SET based inverter which consists of two nominally identical Single-Electron Transistors (SETs) in series that share a common input gate [15]. Each single-electron transistor used in this inverter contains a small aluminum island with a total capacitance  $C_{\Sigma} = 1.6$  fF. On comparison of hybrid SET-MOS inverter [16] and inverter composed of pure SET [15], the voltage gain of hybrid SET-MOS inverter (Fig. 4) has been greatly enhanced. Propagation delay time is further reduced, and the power dissipation has also been reduced notably [17].

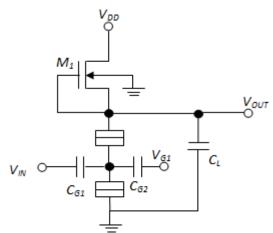

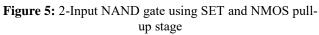

Based on the hybrid SET-MOS inverter design [16], of a 2input NAND gate (Fig. 5) using two series connected SET and depletion type NMOS stage.

## International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Index Copernicus Value (2013): 6.14 | Impact Factor (2014): 5.611

Figure 4: Equivalent circuit of the inverter using SET and depletion type NMOS transistor

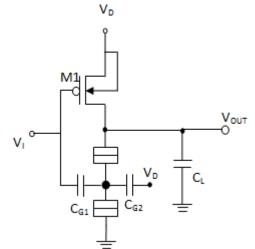

Figure 6: Circuit of Hybrid SET-CMOS Inverter.  $V_I$  is the input voltage and  $V_{OUT}$  is the output voltage

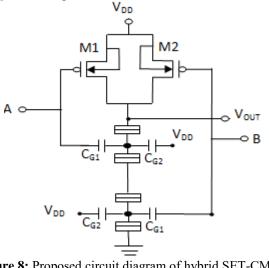

Figure 8: Proposed circuit diagram of hybrid SET-CMOS NAND gate

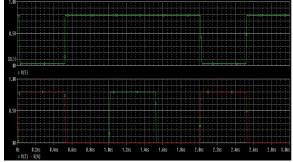

Figure 9: Output waveform of SET-CMOS NAND gate

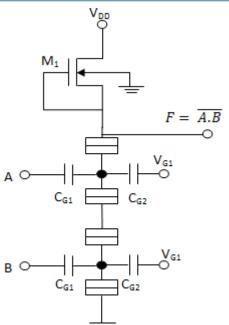

When A = 0.8V and B = 0.8V then  $V_{GS}$  of M1 will be 0.8V and also  $V_{GS}$  of M2 will be 0.8V. Therefore M1 is OFF and M2 is OFF. Since the gate voltage of SET1 is equal to 0.8V and SET2 is equal to 0.8V, both the SET1 is ON.  $V_{OUT}$  is connected to  $V_{DD}$  via M2 and the output is low (Fig. 9).

All the above circuits are simulated in Pspice taking parameters  $C_{G1} = C_{G2} = 1$  aF and  $V_{DD} = 0.8$  V and for PMOS taking  $K_{PO} = 10^{-4} \text{ A/V}^2$ ,  $V_{TO} = 0.01$ V.

# 2. Proposed Hybrid Circuits

## 2.1 Hybrid SET-CMOS inverter proposed

Hybrid SET-CMOS Inverter which is formed by a PMOS transistor as the load resistance of an SET and the pull down transistor is an SET. Since the MIB model is valid for  $|V_{DD}| \leq 3e/C_{\Sigma}$  for single/multiple gate(s) and symmetric or asymmetric SET devices, the bias voltage is taken as 800mV (Fig. 6). The values of the tunnel junction capacitors (C<sub>j1</sub> and C<sub>j2</sub>) have been designed to prevent tunneling due to thermal energy.

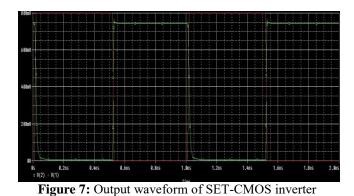

In above Fig. 6 when  $V_I = 0.8V$  (HIGH) then transistor M1 (PMOS) is OFF and SET having both the gate voltages at 0.8V ( $V_{DD}$ ) is ON then  $V_{OUT}$  is 0V (LOW). When  $V_I = 0V$  then transistor M1 is ON and SET is OFF, the  $V_{OUT}$  is 0.8V (HIGH). So it works as inverter (Fig. 7).

## 2.2 Hybrid SET-CMOS NAND proposed

In Fig. 8 hybrid SET-CMOS NAND is designed using parameters with  $C_{G1} = C_{G2} = 1 aF$  and  $V_{DD} = 8mV$ . When A = B=0V then  $V_{GS}$  of M1 will be 0V and also  $V_{GS}$  of M2 will be 0V. Since the gate voltages are less with respect to sources, both M1 and M2 are ON. Since the gate voltage of SET1 is at 0V and SET2 is equal to 0V, both SETs are OFF. With SET1 and SET2 OFF, V<sub>OUT</sub> is connected to V<sub>DD</sub> via M1/M2 and the output is high. When A = 0V and B = 0.8Vthen  $V_{GS}$  of M1 will be 0V and also  $V_{GS}$  of M2 will be 0.8V. Therefore M1 is ON and M2 is OFF. Since the gate voltage of SET1 is equal to 0V and SET2 is equal to 0.8 V, SET1 is OFF and SET2 is ON. V<sub>OUT</sub> is connected to V<sub>DD</sub> via M1 and the output is high. When A = 0.8V and B = 0V then  $V_{GS}$  of M1 will be 0.8V and also  $V_{GS}$  of M2 will be 0V. Therefore M1 is OFF and M2 is ON. Since the gate voltage of SET1 is equal to 0.8V and SET2 is equal to 0V, SET1 is ON and SET2 is OFF.  $V_{\text{OUT}}$  is connected to  $V_{\text{DD}}$  via M2 and the output is high.

## 3. Conclusions

This work explains the basic ideas of Single Electron Transistor (SET) & the concept of hybridization with CMOS technology improve the voltage level at output thus high fan-out. Two hybrid SET-MOS based logic gates (NOT, NAND) are also designed and simulated. Hybrid SET-MOS circuits increases the integrated density, helps in futuristic growth towards nanotechnology. This technology reduces the power consumption of circuits.

# 4. Acknowledgment

The authors are grateful to Dr. V.K. Singh Professor, I.E.T., Lucknow, encouraging me for writing this paper.

# References

- [1] Delsing, P., 1992 One-dimensional arrays of small tunnel junctions, in Single Charge Tunneling. Eds. Grabert, H. and Devoret, M. H., Plenum, New York.

- [2] Nakazato, K., Thornton, T.J., White, J. and Ahmed, H., 1992 Single-electron effects in a point contact using side-gating in delta-doped layers. Applied Physics Letter, Vol. 61, pp. 3145–3147.

- [3] Likharev, K. K., 1988 Correlated discrete transfer of single electron thin ultra small tunnel junctions. IBM Journal of Research and Development, Vol. 32, pp. 144-158.

- [4] Devoret, M.H. and Grabert, H., 1992 Introduction to single charge tunneling in Single Charge Tunneling. Eds. Grabert H. and Devoret M.H. Plenum, New York.

- [5] Kulik, I.O. and Shekhter, R.I., 1975 Kinetic phenomena and charge discreteness in granular media. Soviet Physics Journal of Experimental and Theoretical Physics, Vol. 41, pp. 308–316.

- [6] Likharev, K. K., 1999 Single-electron devices and their applications. Proceedings of the IEEE, Vol. 87, pp. 606–632.

- [7] Durrani Zahid, A.K., 2003 Coulomb Blockade, Single-Electron Transistors and Circuits in Silicon. Physica E, Vol. 17, pp. 572-578.

- [8] Klunder, R. H. and Hoekstra, J., 2001 Circuit Architecture Solution for Background Charge Fluctuations in Single Electron Tunneling Transistors. Proceedings of European Conference on Circuit Theory and Design (ECCTD), Vol. 3, pp. 213–216.

- [9] Wasshuber, C., Kosina, H. and Selberherr, S., 1997 SIMON – A simulator for single-electron tunnel devices and circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 16, pp. 937–944.

- [10] Khoury, M., Gunther, A., Milicic, S., Rack, J., Goodnick, S.M., Vasileska, D., Thornton, T.J. and Ferry ,D.K., 2000 Single-Electron Quantum Dots in Silicon MOS Structures. Applied Physics A, Vol. 71, pp. 415-421.

- [11]Yu, Y. S., Hwang, S. W. and Ahn. D., 1999 Macromodeling of Single-Electron Transistors For Efficient Circuit Simulation. IEEE Transactions on Electron Devices, Vol. 46, pp. 1667-1671.

- [12] Amakawa, S., Majima H., Fukui, H., Fujishima, M. and Hoh, K., 1998 Single-electron circuit simulation. IEICE Transactions on Electronics, Vol. E81-C, pp. 21–29.

- [13] Likharev K.K., Bakhvalov N.S., Kazacha G.S. and Serdyukova S.I., 1989 Single electron tunnel junction array: An electrostatic analog of the Josephson transmission line. IEEE Transactions Magazine, Vol. 25, pp. 1436-1439.

- [14] Tucker, J.R., 1992 Complementary digital logic based on the Coulomb blockade. Journal of Applied Physics, Vol. 72, pp. 4399–4413.

- [15] Lientschnig, G., Weymann, I., and Hadley P., 2003 Simulating Hybrid Circuits of Single- Electron Transistors and Field-Effect Transistors. Japanese Journal of Applied Physics, Vol. 42, pp. 6467–6472.

- [16] Li, Q., Cai, L., Zhou, Y., Wu G. and Wang S., 2008 Design and simulation of logic circuits by combined single-electron MOS transistor structures. Proceedings of IEEE International Conference on Nano/Micro Engineered and Molecular Systems, pp. 210–214.

- [17] Venkataratnam, A. and Goel, A. K., 2008 Design and simulation of logic circuits with hybrid architectures of single-electron transistors and conventional MOS devices at room temperature. Microelectronics Journal, Vol. 39, pp. 1461–1468.