# Enhanced Gain Constant Gm Low Power Rail to Rail Operational Transconductance Amplifier for Wideband Application

# Sakshi Dhuware<sup>1</sup>, Mohammed Arif<sup>2</sup>

<sup>1</sup>M-Tech.4<sup>th</sup> sem., GGITS Jabalpur, Madhya Pradesh, India

<sup>2</sup>Professor, GGITS Jabalpur, Madhya Pradesh, India

**Abstract:** A modification to the recycling current rail-to-rail operational transconductance amplifier is presented. The proposed amplifier has the benefit of delivering the better performance while consuming less amount of the power as compared to the conventional rail-to-rail amplifier .In this paper a constant current technique depending on the input stage is proposed. Using this method, the rail to rail amplifier processes low power and occupies a small chip area. The proposed amplifier was implemented in 45nm CMOS technology. Simulated results show that the proposed design achieves 76.6dB DC gain, 331.2 MHz GBP (gain bandwidth product) and the power consumption is goes up to 15.03uW at 1.6V supply voltage.

Keywords: OTA, rail to rail, common mode, transconductance amplifier, constant Gm control

#### **1.Introduction**

HIGH performance Analog to Digital Converters (ADC) and switched capacitor (SC) filters require Operational Transconductance Amplifiers (OTAs) that has both high DC gain and a high unity gain bandwidth (UGB). The advent of deep sub-micron technologies enables increasingly high speed circuits. As the technology scales down, the intrinsic gain  $g_m r_o$  of the transistor decreases which makes it difficult to design OTAs with high DC gain. In low voltage CMOS process, Folded Cascode (FC) amplifier is one of the most preferred architectures for both single stage and for the first stage of the multi-stage amplifiers due to its high gain and reasonably large output signal swing. Moreover, the FC with PMOS input pair is preferred over its NMOS counterpart due to its higher non-dominant poles and lower flicker noise [1], [2].

A number of techniques have been proposed in the literature to enhance the gain of the FC OTA. One of these techniques presented in [3], [4] enhances the DC gain by providing an additional current path at the cascode node. This converts the current source into active current mirror which raises the output current to be above its quiescent value during slewing. Another technique proposed in [5], enhances the DC gain and UGB by modifying the bias current sources of the FC OTA. These current sources do not contribute to DC gain. A recycling technique is proposed to overcome this disadvantage.

This OTA is referred to as Recycling Folded Cascode (RFC). In [6], further enhancement in the DC gain and UGB of the RFC OTA is obtained using Improved Recycling structure and is termed as IRFC OTA. An enhanced IRFC (EIRFC) OTA is proposed in this paper, by adopting the technique proposed in [3], [4] for the FC OTA. The performance of the two OTAs (IRFC and EIRFC) are evaluated through simulation and compared.

#### 2. Transconductance

Transconductance (Gm) is the property of certain electronic components. The ratio of the change in current at the output port to the change in voltage at the input port is called as transconductance. Some time it is written as  $g_m$ . For direct current, transconductance is defined as follows:

$$g_m = \frac{\Delta I_{out}}{\Delta V_{in}}$$

For small signal alternating current, the definition is simpler:

$$g_m = \frac{i_{\text{out}}}{v_{\text{in}}}$$

# **3.**Operational Transconductance Amplifier (OTA)

OTA is a voltage controlled current source, its takes the difference of the two input voltages for the current conversion.

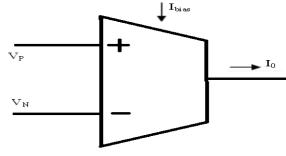

Figure 1: Ideal model of OTA

The output current  $I_0$  of the ideal OTA can be expressed by Equation:

$I_0 = g_m (V_P - V_N)$

Where  $V_P$  and  $V_N$  are the voltages of positive and negative terminal [7].

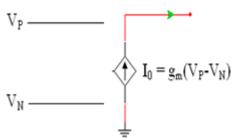

Figure 2: Equivalent circuit of OTA

The operational transconductance amplifier (OTA) is a vital analog building block and for many applications is the largest and most power consuming block [8]. In recent years, the need for circuits operating at low voltage has increased due to scaling of devices, especially in deep submicron technology [9]. However, the conventional RtR amplifiers usually consume more power than general other amplifiers because of the increased current path formed by the additional input pairs. Therefore, to satisfy more and more low power applications, it becomes important to reduce the power budgets [10].

In previous paper, recycling current rail to rail (RCRtR) operational transconductance amplifier has delivering the same performance while consuming less power compared to the conventional rail to rail amplifier [11]. In this paper, a modification to the recycling current rail to rail amplifier is presented. The proposed amplifier has giving better performance and consuming a fraction of the power as compared to the recycling current rail-to-rail operational transconductance amplifier.

The design procedure is based on following main parameters: noise, phase margin, gain, load capacitance, slew rate, input common mode range, common mode rejection ratio.

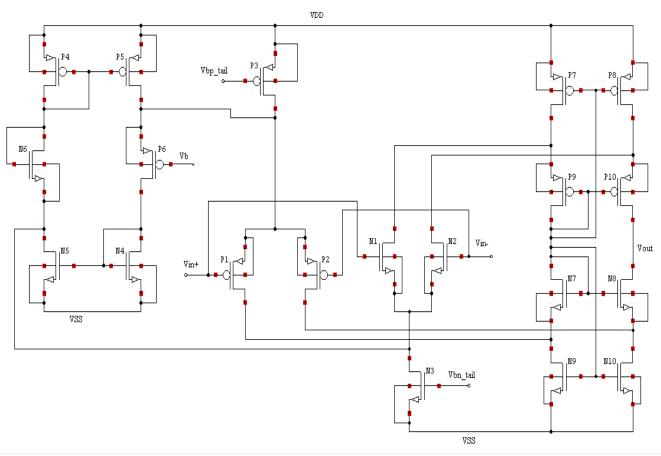

## 4. Proposed Rail to Rail Amplifier

As the input stage, the differential amplifier is used for operational amplifiers .the problem is that it behaves as a differential amplifier only over a limited range of common – mode input. Therefore, to make the operational amplifier versatile, its input stage should work for RtR common- mode input range The most common method to achieve this range is to use a complementary differential amplifier at the input stage. Where N1, N2 and P1, P2 constitute the n- type and ptype differential input pairs, respectively shown in fig.4.

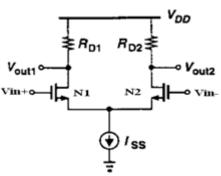

The N-MOS differential pair is shown in fig 3.in which input pair, N1 & N2, is able to reach the positive supply rail. The range extends from the positive supply to (Vgs, n + VDsat, b) above the negative supply.

Figure 3: NMOS differential pair

This minimum voltage is needed to keep the NMOS differential pair and the tail current source in saturation. The role of tail current source is to suppress the effect of input CM level variations on the operation of N1 and N2 and the output level.

A similar analysis can be carried out for the PMOS differential pair. The proposed circuit is shown in fig. 4. Rail-to-rail input means that input signal can be anywhere between the supply voltages with all the transistors in the saturation region. To have a RtR common mode input range, two complementary differential pairs are required to form the input stage .N-channel input pair,N1 & N2, is able to reach the positive supply rail while the P- channel input pair, P1 & P2, is able to reach the negative supply rail. The constant-gm control circuit is achieved through transistor N3-N6 and P3-P6.this circuit maintains a constant tail current when either of the two differential pairs goes off. Vbn\_tail and Vbp\_tail is the control voltage of N3 and P3 MOSFET.

$\begin{array}{l} g_{m,\,np\,=}\,g_{m,\,n}\,+\,g_{m,\,p} \\ g_{m,\,n}\,=\,\sqrt{2}\mu_n C_{ox}(W/L) I_D \end{array}$

Where  $g_{m, n}$  and  $g_{m, p}$  is the transconductance of NMOS and PMOS respectively and  $\mu_n$  is the mobility of NMOS,  $C_{ox}$  is oxide capacitance.

In order to describe the operation of constant –gm control circuit, first, it is supposed that PMOS and NMOS differential pairs are both in operation and the transistor P3 and N3 as the tail current source provide the same current for PMOS and NMOS differential pairs respectively.

The constant gm circuit (P4-P6) and (N4-N6) are used to control transconductance. Through adjusting the ratio of width to length of the input differential pairs, the tail current can be kept constant and stable. The input differential pairs are kept biased in saturation region under all conditions.

#### International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Impact Factor (2012): 3.358

Figure 4: Proposed Rail To Rail Operational Transconductance Amplifier

## **5. Simulation and Result**

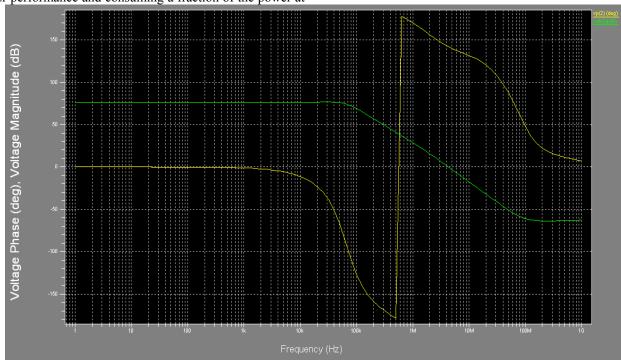

The proposed rail to rail operational transconductance amplifier is designed to operate with 1.6v power supply, and fabricated in a standard 45nm CMOS process with 15uW power consumption. The proposed amplifier has giving better performance and consuming a fraction of the power at less Power supply as compared to the recycling current railto-rail operational transconductance amplifier. The gain and phase margin of this RtR is 76.6 dB and 38.03 (deg) .This method provide improved gain, GBW, slew rate and FOM at less power supply compare to RCRtR. Simulation result summary is shown in below table I.

Figure 5: Gain (dB) and phase margin (deg) versus frequency (Hz)

## International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Impact Factor (2012): 3.358

| Table 1: Simulation Result Summary |                                                                                             |

|------------------------------------|---------------------------------------------------------------------------------------------|

| RCRtR                              | Thispaper                                                                                   |

| 1.8                                | 1.6                                                                                         |

| 63.8                               | 76.6                                                                                        |

| 23.4                               | 200                                                                                         |

| 168.1                              | 331.2                                                                                       |

| 8                                  | 8                                                                                           |

| 304                                | 9.39                                                                                        |

| 2212                               | 3676.59                                                                                     |

|                                    | RCRtR           1.8           63.8           23.4           168.1           8           304 |

## **Table 1:** Simulation Result Summary

## 6. Conclusion

The proposed RtR operational transconductance amplifier does not require an extra circuit and drastically reduces design complexity and power consumption. It has been demonstrated that the proposed circuit can boost the gain, GBP and slew rate using 1.6 supply voltage.

## References

- [1] Behzad Razavi, "Design of Analog CMOS Integrated Circuit", *Tata McGraw Hill* 2001.

- [2] Sudhir.M.Mallya, Joseph.H.Nevin, "Design Procedures for a fully differential Folded Cascode CMOS operational Amplifier", *IEEE Journal of Solid-State Circuits*, Vol.24, No.6, December 1989,pp 1737-1740.

- [3] Katsufumi Nakamura and L. Richard Carley, "A Current – based positive-feedback technique for efficient cascode bootstrapping", *Symposium on VLSI Circuits Digest Technical Papers*, May 1991, pp 107-108.

- [4] K.Nakamura and L.R. Carley, "An enhanced fully differential folded cascode op-amp", *IEEE Journal of Solid-State Circuits*, Vol.27, No.4 APR.1992. pp.563-568.

- [5] RidaS.Assaad and Jose Silva-Martinez, "The Recycling folded cascode: A general enhancement of the folded cascode amplifier", *IEEE Journal of Solid State Circuits*, Vol.44, No.9, September 2009, pp 2535-2542.

- [6] Y.L.Li, K.F.Han, X.Tan, N.Yan, and H.Min, "Transconductance enhancement method for operational transconductance amplifiers", *IET Electronics Letters*, Vol.46, No.9, September 2010, pp 1321-1322.

- [7] Abhay Pratap Singh, Sunil Kumar Pandey, Manish Kumar, "Operational Transconductance Amplifier For Low Frequency Application," *International Journal Computer Technology & Applications*, Vol.3 (3), May-June 2012.

- [8] Sansen, Analog design essentials, Springer, Dordrecht, the Netherlands, 2006.

- [9] Katsufumi Nakamura, L. Richard Carley, "An Enhanced Fully Differential Folded-Cascode OP Amp," *IEEE Journal of Solid-State Circuits*, Vol. 27, No.4, 1992.

- [10] RidaS.Assaad, Jose Silva-Martinez, "Enhancing general performance of folded-cascode amplifier by recycling current," *ELECTRONICS LETTER*, VOL. 43, NO. 23, November 2007.

- [11] Xiao Zhao, Huajun Fang And Jun Xu "A Low Power Constant-Gm Rail-To-Rail Operational Trans-Conductance Amplifier By Recycling Current" *Electron Devices And Solid- State Circuits (EDSSC) IEEE International Confrence*, November 2011.

- [12] Suparshya Bbu Sukhavasi, Susrutha Babu Sukhavasi, Dr. Habibulla Khan ,S R Sastry Kalavakolanu, Vijaya Bhaskar Madivada, Lakshmi Narayana Thalluri, "Design Of Low Power Operational Amplifier By Compensating The Input Stage", *International Journal* Of Enginnering Research And Applications (IJERA), VOL.2, PP.1283-1287, Mar-April 2012.

- [13] Razavi, B. Design of analog CMOS integrated circuits. *McGraw-Hill*(2001).

- [14] F. Roewer and U. kleine, "A Novel Class of Complementary Folded-Cascode Opamps for Low Voltage," Circuits, VOL. 37, NO. 8, August 2002.

- [15] Laber, C. A., & Gray, P. R. (1988). "A positive transconductance amplifier with applications to high high-Q CMOS switched-capacitor filters," *IEEE Journal of Solid State Circuits*, 23(6), 1370–1378.

- [16] Lloyd, J.; Hae-Seung Lee. "A CMOS op amp with fully differential gain enhancement" *IEEE Transaction on Circuit and System II: Analog and Digital Signal Processing*, Vol.41, NO. 3 MARCH 1994.

- [17] Soni.H, Dhavse.N, "Design of Operational Transconductance Amplifier using 0.35µm technology", *International Journal of Wisdom Based Computing* vol 1, pp28-31, 2011.

## **Author Profile**

Sakshi Dhuware is currently doing M.Tech.in Embedded System and VLSI Design from Gyan Ganga Institute of Technology & Science, Jabalpur.

**Mohammed Arif** is working as a professor in Electronics and Communication Engineering department in Gyan Ganga Institute of Technology & Science, Jabalpur.