# Low Power 8 Bit quantum ALU Implementation Using Reversible Logic Structure

# Vijay G. Roy<sup>1</sup>, P. R. Indurkar<sup>2</sup>, D. M. Khatri<sup>3</sup>

<sup>1, 2, 3</sup>RTMNU, Nagpur University, B.D.C.O.E., Sevagram, Wardha, M. S., India

Abstract: Reversible computation emerged as a result of the utilization of quantum mechanics principles in the development of a universal computing machine. Reversible computing has a strong impact on digital logic designs. Reversible logic units are required to recover the state of inputs from its outputs. It will have an impact on instruction sets and high-level programming languages as well. Finally, these will also have to be reversible to produce optimal efficiency. Upcoming advancements in reversible logic allow new methods for computer architectures using improved quantum computer algorithms. Important contributions have been made in the literature based on the design of reversible logic gate structures and arithmetic units, however, there are not many efforts directed towards the design of reversible ALUs. In this work, novel programmable reversible logic gates are presented and utilized, and its implementation in the design of a reversible Arithmetic Logic Unit is illustrated. Using 1 bit ALU, an 8 bit ALU has been designed and verified. This proposed 8 bit ALU is also compared against the existing 8 bit ALU with reference to few important parameters such as power dissipation and propagation delay. The major advantage of proposed ALU is the increased number of operations with certain number of select inputs with low power consumption. This ALU can be utilized in low power VLSI design, nanotechnology, quantum computing and optical computing.

Keywords: Quantum computing, Reversible logic structures, Arithmetic logic unit, VLSI, Low power dissipation.

#### 1. Introduction

Reversible logic has intense potential to have extended applications in future emerging technologies. Reversible logic is very useful for the construction of low power, low loss computational structures which are very much significant for the construction of arithmetic circuits used in quantum computation, nanotechnology and other low power digital circuits. Nowadays, several researchers have directed their efforts on the design and synthesis of efficient reversible logic circuits. The most important reversible gates used for reversible logic synthesis are Feynman Gate, Fredkin gate, HNG gate and MG gate.

#### 2. Reversible Logic

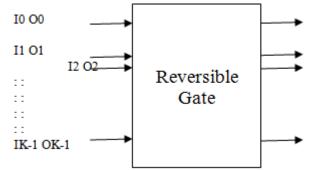

Reversibility means that no relative information about the computational states can ever be lost, so we can recover at any earlier stage by computing in backward direction or uncomputing the results. This is said to be logical reversibility. A reversible logic gate is a k-input and k-output (k\*k) device that maps each possible input vector pattern into a unique output vector pattern as shown in fig.1 where I0,I1,I2,....IK-1 are the input vectors and O0,O1,O2,.....OK-1 are the output vectors.

#### **3. Reversible Gates**

A reversible logic gate is an n-input and n-output logic device having one-to-one mapping. This helps to determine the outputs from their inputs and also the inputs can be uniquely and successfully recovered from the outputs.

The Feynman gate is the basic fundamental reversible logic gate. It functions as a two input reversible gate with outputs P = A and Q = A XOR B. The gate flips the target qubit if and only if the control qubit is 1. The resulting value of the second qubit corresponds to the result of a conventional XOR gate. When the second input is 0, the Feynman gate may be used to produce a duplicate of input signal. Its quantum configuration is shown in figure 2.

$$A = A$$

$B = A \oplus B$

Figure 2: Quantum representation of Feynman gate

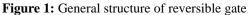

The integrated 2\*2 qubit gate is obtained by implementing a Feynman gate with either a Controlled-V or Controlled V+ gate. The XOR output of the Feynman gate functions as the control input of the Controlled-V or V+ gate. Its quantum cost is taken as 1, and is shown in figure 3.

Figure 3: Quantum representation of integrated Qubit gates

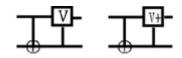

The Fredkin gate is a 3\*3 reversible logic gate whose quantum representation is shown in figure 4. The outputs are related with the inputs as follows: P = A, Q = A'B+AC and R = AB+A'C. Therefore, the outputs works as a multiplexed

output of the two data inputs based on the control input. It is constructed using 2 Feynman gates, a Controlled-V gate and two integrated qubit gates.

Figure 4: Quantum representation of Fredkin gate

The Toffoli gate is a 3\*3 reversible logic gate whose quantum representation is shown in figure 5. The outputs map to the inputs in this manner: P = A, Q = B and R = AB XOR C.

Figure 5: Quantum representation of Toffoli gate

The Peres gate is a 3\*3 reversible logic gate whose quantum representation is shown in figure 6. The outputs are related with the inputs in this manner: P = A, Q = A XOR B and R = AB XOR C.

Figure 6: Quantum representation of Peres gate

#### 4. One Bit ALU Implementation

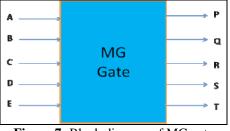

We propose the design of a 5\*5 programmable reversible logic gate structure utilized in the implementation of an ALU. The cost of the MG is 7, and the worst-case delay is 7. The truth table of MG gate is given below which shows the operations obtained according to combinations of select inputs.

Figure 7: Block diagram of MG gate

MG gate has 5 inputs i.e. A, B, C, D, and E and 5 outputs i.e. P, Q, R, S, and T. Output vectors have following expressions: P = A, Q = A XOR B, R = (A XOR B) XOR C, S = AB XOR D and T = ((A XOR B) XOR E) XOR (AB XOR D)

| Table 1: Truth table of MG gate |   |   |          |          |         |  |

|---------------------------------|---|---|----------|----------|---------|--|

| С                               | D | E | R        | S        | Т       |  |

| 0                               | 0 | 0 | A XOR B  | A AND B  | A OR B  |  |

| 0                               | 0 | 1 | A XOR B  | A AND B  | A NOR B |  |

| 0                               | 1 | 0 | A XOR B  | A NAND B | A NOR B |  |

| 0                               | 1 | 1 | A XOR B  | A NAND B | A OR B  |  |

| 1                               | 0 | 0 | A XNOR B | A AND B  | A OR B  |  |

| 1                               | 0 | 1 | A XNOR B | A AND B  | A NOR B |  |

| 1                               | 1 | 0 | A XNOR B | A NAND B | A NOR B |  |

| 1                               | 1 | 1 | A XNOR B | A NAND B | A OR B  |  |

The MG gate is utilized in the implementation of a novel arithmetic logic unit. The ALU, in addition to producing the same logical calculations as the MG, is able to perform addition and subtraction by utilizing the HNG gate and store less-than operation.

Figure 8: RTL view of 1-bit ALU

The operation code of 1-bit ALU is shown below which represents eight operations with certain combinations of six select inputs.

| Select Inputs |    |            |            |            |            |            | Hex  | Operat |

|---------------|----|------------|------------|------------|------------|------------|------|--------|

| <b>S</b> 6    | S5 | <b>S</b> 4 | <b>S</b> 3 | <b>S</b> 2 | <b>S</b> 1 | <b>S</b> 0 | Code | ion    |

| 0             | 1  | 1          | 0          | 0          | 0          | 0          | 30H  | AND    |

| 0             | 1  | 1          | 0          | 1          | 1          | 0          | 36H  | NAND   |

| 0             | 0  | 0          | 1          | 1          | 0          | 0          | 0CH  | OR     |

| 0             | 0  | 0          | 0          | 1          | 1          | 0          | 06H  | NOR    |

| 0             | 1  | 0          | 0          | 1          | 0          | 0          | 24H  | XOR    |

| 0             | 1  | 0          | 0          | 1          | 1          | 0          | 26H  | XNOR   |

| 0             | 0  | 1          | 1          | 0          | 0          | 0          | 18H  | ADD    |

| 0             | 0  | 1          | 1          | 1          | 0          | 0          | 1CH  | SUB    |

Table 2: Operation codes of 1-bit ALU

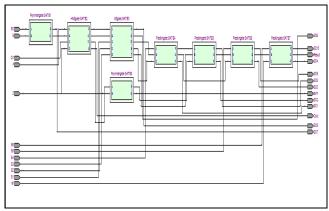

#### 5. Eight Bit ALU Implementation

By using 1-bit ALU described above an 8-bit ALU has been designed and verified. This 8-bit ALU will also produce the same operations on two 8-bit inputs as in case of 1-bit ALU. The 8-bit ALU reflects the select input combinations for 8-bit vector inputs generating same results.

#### International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Impact Factor (2012): 3.358

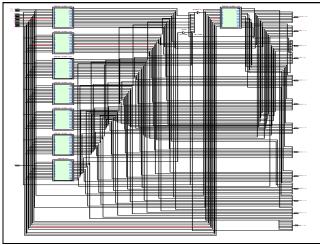

Figure 9: RTL view of 8-bit ALU

# 6. Simulation Results

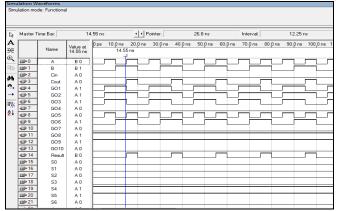

The 1-bit ALU and 8-bit ALU are simulated and their simulated waveforms are verified by using QUARTUS II simulation software in VHDL. The simulation results of 1-bit ALU is shown below where select inputs S4 and S5 taken as logic 1 while other select inputs taken as logic 0. This makes the op-code as 30H which indicates AND operation as mentioned in operation codes of 1-bit ALU. The complete AND operation truth table has been verified by its functional simulation as shown in figure.

Figure 10: Simulation waveforms of 1-bit ALU

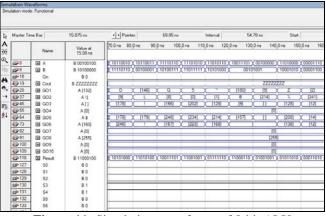

The simulation result of 8-bit ALU is shown in figure below where select inputs S3 and S4 taken as logic 1 while other select inputs taken as logic 0. This makes op-code as 18H which indicates ADD operation as mentioned in operation codes of 8-bit ALU. The complete ADD operation can be verified by its functional simulation as shown in figure below.

Figure 11: Simulation waveforms of 8-bit ALU

# 7. Comparison

The comparative analysis of proposed ALU with respect to the existing ALU is given below. This comparison is mainly based upon important parameters such as power dissipation and propagation delay.

| Sr.<br>No. | Parameters                      | Existing 8 bit<br>ALU1 | Proposed 8 bit<br>ALU |

|------------|---------------------------------|------------------------|-----------------------|

| 1          | Total thermal power<br>estimate | 270.78 mW              | 265.81 mW             |

| 2          | Core dynamic power dissipation  | 18.49 mW               | 14.71 mW              |

| 3          | Core static power dissipation   | 39.63 mW               | 39.63 mW              |

| 4          | I/O thermal power dissipation   | 212.66 mW              | 211.48 mW             |

| 5          | Max. propagation delay          | 9.270 ns               | 19.506 ns             |

| 6          | Min. propagation delay          | 3.015 ns               | 4.092 ns              |

| 7          | Number of operations            | 6                      | 8                     |

Table 3: Comparative analysis of 8-bit ALU

After analyzing the above comparison we can conclude that the proposed ALU is more power efficient than the existing one at the cost of slight increase in propagation delay.

# 8. Conclusions

A novel 5\*5 programmable MG gate was proposed and verified that may calculate of AND, NAND, OR, NOR, OR and XNOR depending on the inputs from the programmer. The proposed MG gate has been implemented in the design of a novel quantum arithmetic logic unit, and its design has been compared with the existing work in programmable ALU design. The novel 1-bit ALU required only minimal increase in quantum cost and delay due to the MG design, which also allowed for increased functionality for the computing machine. An ALU is a major component of a computing device and is the core component of central processing unit. Moreover, it is the heart of the instruction execution portion of every computer. An ALU is a multifunctional circuit that conditionally performs one of several possible functions on two operands A and B depending on the combinations of selection inputs. The low power dissipation of proposed ALU makes it more useful in less power requirement applications.

# 9. Future Scope

This ALU can be used in applications such as quantum computing, nano-technology, optical computing, low power VLSI designs etc. The extended operations will be more useful for doing complex logic designs. Many ASICs based projects could be possible by using the proposed ALU design.

# 10. Acknowledgement

The authors would like to acknowledge their friends, colleagues and well-wishers for their continuous support and positive encouragement. They also want to convey their sincere gratitude towards the Principal of B.D.C.O.E., Dr. M. A. Gaikwad for providing excellent academic and research infrastructures which helps them to focus their ideas in a right perspective.

#### References

- W. David Pan and Mahesh Nalasani, "Reversible logic," 2005 IEEE potentials pp. 38-41

- [2] Himanshu Thapliyal and M. B. Shrinivas, "Novel Reversible 'TSG' Gate and Its Application for Designing Components of Primitive Reversible Quantum ALU,"2005 IEEE ICICS pp. 1425-1429.

- [3] Mingming Zhang, Shuguang Zhao, Xu Wang. Poor, "Multi-objective Reversible Logic Gate-level Evolutionary Synthesis Using Multi-objective Adaptive Discrete Differential Evolution,"2009 Third International Symposium on Intelligent Information Technology Application pp. 533-536.

- [4] Himanshu Thapliyal and Nagarajan Ranganathan, "Reversible Logic Based Concurrent Error Detection Methodology for Emerging Nano circuits," 2010 IEEE proceedings of 10th International Conference on nanotechnology pp. 217-222.

- [5] Mahapatro, Sisira Kanta Panda, Jagannath Satpathy, Meraj Saheel, "Design of Arithmetic Circuits Using Reversible Logic Gates and Power Dissipation Calculation," 2010 International Symposium on Electronic System pp. 85-90.

- [6] Prashant R. Yelekar and Prof. Sujata S. Chiwande, "Introduction to Reversible Logic Gates & its Application,"2nd National Conference on Information and Communication Technolgy (NCICT) 2011 pp. 5-9.

- [7] Zhijin Guan, Wenjuan Li, Weiping Ding, Yueqin Hang Lihui Ni, "An Arithmetic Logic Unit Design Based on Reversible Logic Gates," 2011 IEEE pp. 925-931.

- [8] Y. Syamala and A.V. N. Tilak, "Reversible Arithmetic Logic Unit," IEEE 2011 pp. 207-211.

- [9] Matthew Morrison and Nagarajan Ranganathan, "Design of a reversible ALU based on Novel Programmable Reversible Logic Gate Structures,"2011 IEEE Computer Society Annual Symposium on VLSI pp. 126-131.

- [10] Himanshu Thapliyal and Nagarajan Ranganathan, "Reversible Logic: Fundamentals and Applications in Ultra-low power, Fault testing and Emerging Nanotechnologies, and Challenges in future," Tutorial

T2 2012 25th International Conference on VLSI Design pp.13-15.

- [11] Ismo Hanninen and Jarmo Takala, "Irreversibility Induced Density Limits and logical Reversibility in Nanocircuits," 2012 IEEE/ACM NANOARCH pp. 50-54.

- [12] Rakshith T. R. and Rakhshith Saligram, "Parity Preserving Logic based Fault Tolerant Reversible ALU," 2013 IEEE Conference on Information and Communication Technologies (ICT 2013) pp. 485-490.

- [13] Vijay G. Roy, Prof. P. R. Indurkar, Prof. Mrs. D. M. Khatri, "A Survey on Design Approaches towards Quantum ALU using Reversible Logic Structures," International Journal of Scientific & Engineering Research, Volume 5, Issue 1, January-2014 pp.1372-1376.

- [14] Vijay G. Roy, Prof. P. R. Indurkar, Prof. Mrs. D. M. Khatri, "A Cost Effective Quantum ALU Design Based On Reversible Logic Structures," International Conference on Quality Upgradation in Engineering, Science and Technology April-2014.

# **Author Profile**

**Vijay G. Roy is** B.E. (Electronics) currently doing M. Tech (VLSI) in B.D.C.O.E., Sevagram (Wardha), Maharashtra, India

**Prof. P. R. Indurkar** has done B.E. (Electronics and Power), M. Tech (Electronics) currently working as Associate Professor, M. Tech co-ordinator in B.D.C.O.E., Sevagram, Department of electronics and telecommunication Engg, BDCOE, Sevagram (Wardha), Maharashtra, India, 20 years experience,

**Prof. Mrs. D. M. Khatri** has done B.E. (Electronics and Power), M. Tech (Electronics) currently working as Assistant Professor, in B.D.C.O.E., Sevagram, Department of electronics and telecommunication Engg, BDCOE, Sevagram (Wardha), Maharashtra, India, 7 years experience