# Implementation of a Pacemaker for Biomedical Application

# Roopa T<sup>1</sup>, Manjula B. M<sup>2</sup>, Dr. Chirag Sharma<sup>3</sup>

<sup>1, 2, 3</sup> Department of Electronics and Communication Engineering, Nitte Meenakshi Institute of Technology, Bangalore-560064, India

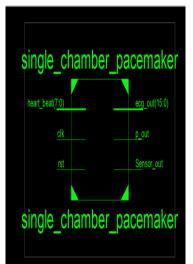

Abstract: In this project work A state machine approach has been followed to design and implement a single and dual chamber pacemaker in response to different heart beats from 35bpm-125bpm. The heart of the pacemaker system rests in the pulse generator which forms the major portion of the project. It has been developed using Verilog and implemented in hardware using FPGA. In the FSM, first an input event is detected. Once this input is detected a timer is set which will be the time between heartbeats, thus giving 35-125 heartbeats per minute. This pacemaker responses only when the QRS wave is low or high in compared to normal ECG wave. The designing and verification is done through verilog on Xilinx 14.1. Also, ECG signal is generated in modelsim 10.1b. The pacemaker response is verified with various heart beats from 35-125bpm.

Keywords: ECG, pacemaker, single chamber pacemaker, dual chamber pacemaker, verilog.

# 1. Introduction

Pacemakers were first introduced in the 1950s, with only few transistor used in the device. Technology has advanced greatly and there are over tens of millions of transistor in today's implantable pacemaker system. A cardiac pacemaker is used to treat bradycardia (a heart rate that is too slow) and tachycardia(a heart rate that is too slow). This pacemaker monitor the heart's rate (how fast it beats) and rhythm (the pattern in which it beats), and provides electrical simulation when the heart does not beat or beats too slowly or too high.

The paper briefly introduces the general aspects of single and dual chamber pacemaker Structure and functions. Generating ECG signal in Matlab. Extracting these signal coefficients for different heart beat from 35-125bpm and storing in LUT and generating this signal in modelsim. This designed pacemaker works only when the QRS wave is low or high in compared to normal ECG wave. Depending upon the heart beats from 35-125bpm with ecg signal the single and dual chamber chambers will turn on or off.

# 2. Implementation

#### 2.1 ECG signal generation

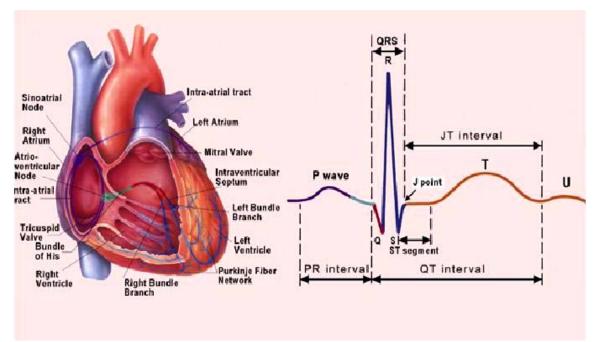

ECG is used to measure the heart's electrical conduction system. It picks up electrical impulses generated by the polarization and depolarization of cardiac tissue and translates into a waveform. The waveform is then used to measure the heart rate. It records any problems with the heart's rhythm, and the conduction of the heart beat through the heart which may be affected by underlying heart disease.

Figure 2.1: The ECG signal generation

#### International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Impact Factor (2012): 3.358

ECG signal can be generated using Fourier series which satisfies dirichlet's condition. Any periodic functions which satisfy dirichlet's condition can be expressed as a series of scaled magnitudes of sin and cos terms of frequencies which occur as a multiple of fundamental frequency.

ECG signal is periodic with fundamental frequency determined by the heartbeat. It also satisfies the dirichlet's conditions:

- Single valued and finite in the given interval

- Absolutely integrable

- Finite number of maxima and minima between finite intervals

- It has finite number of discontinuities

Hence Fourier series can be used for representing ECG signal. This signal can be generated using matlab for different heart beats from 35-125bpm. These coefficients are extracted and stored in look up table (LUT). For these values verilog code has been developed to extract ECG waveform ECG specification: ECG: 0-100hz

- ECG amplitude range=0.05-3V

- Heart amplitude~0.5mv

- Normal heart beat range= 60-90 bpm

- Bradycardia heart beat range=below 60bpm

- Tachycardia heart beat range= above 95bpm

- P duration < 0.12 sec

- P amplitude < 0.25 mv

- QRS duration  $\leq 0.11$  sec

- Qrs wave amplitude <2.4mV

- PR interval=0.12 0.20 sec

- Qrs wave duration=0.06 0.10 sec

- S wave amplitude<0.35mv

- T wave amplitude <=0.35mV

# Table 1: ECG signal output for different heart beats

| Heart beats | clk | rst | validin | Sensor_ |

|-------------|-----|-----|---------|---------|

| (8bit)      |     |     |         | out     |

| 35          | 1   | 1   | 0       | 0       |

| 35-55       | 1   | 0   | 1       | 0       |

| 65-85       | 1   | 0   | 1       | 1       |

| 95-125      | 1   | 0   | 1       | 0       |

#### 2.2. Single Chamber Pacemaker

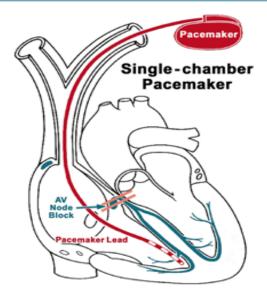

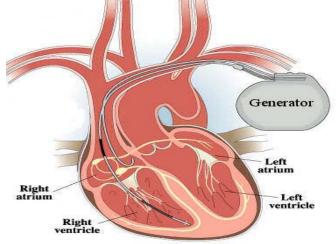

A single chamber pacemaker is one which only one of the two chambers of the heart atrium or ventricles is paced, since ventricle have stronger muscle and they have to pump the blood to longer distance compared to atria i.e. sensing and pacing is done at ventricle. The wires in a single-chamber pacemaker carry pulses between the right ventricle (the lower right chamber of your heart) and the generator.

Figure 2.2: Single chamber pacemakers

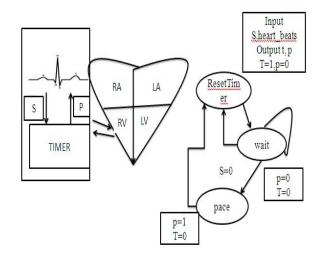

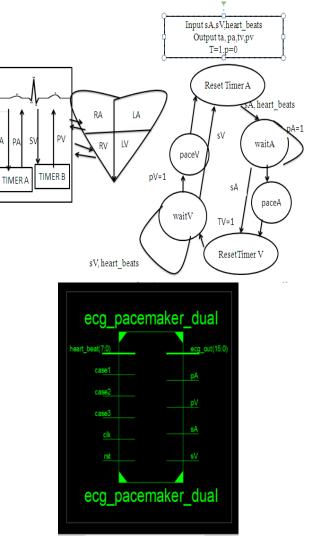

#### 2.3 State diagram for single chamber pacemaker

The state machine designed for this pacemaker consists of three states: ResetTimer, Wait and Pace. The system gets the input from the ECG signal through the sensor if presence of QRS wave is sensed or not. Depending on 'S' it stays in the wait state or goes to the pace state. When normal QRS wave sensed then the pacemaker resets the timer.

So the general flow of a complete cycle of the pacemaker goes in the following path:

Reset Timer → Wait → Pace

Inputs:

**S:** sensing parameter: 1 if normal QRS wave is detected else 0.

**Heart\_beats**: the number of heart beats per minute , 35-55bpm, heart\_beats=1; 65-85bpm, heart\_beats=0; 95-125bpm, heart\_beats=1

**Outputs:**

**T**: output to timer: 1 if timer is to be reset.

**P**: output to heart: 1 if pacing needs to be done.

Figure 2.3: State diagram of single chamber pacemaker

| T     | <b>Table 2:</b> State table of single chamber pacemaker |       |             |        |        |  |  |

|-------|---------------------------------------------------------|-------|-------------|--------|--------|--|--|

| state | function                                                | input | input       | output | output |  |  |

|       |                                                         | S     | Heart_beats | Р      | Т      |  |  |

| Α     | Wait                                                    | 0     | 0           | 0      | 0      |  |  |

| В     | Pace                                                    | 0     | 1           | 1      | 0      |  |  |

| C     | Reset                                                   | 1     | 0           | 0      | 1      |  |  |

|       | Timer                                                   | 1     | 1           | 0      | 1      |  |  |

Table 2: State table of single chamber pacemake

#### 2.2. Dual Chamber Pacemaker

A pacemaker with pacing electrodes in both the right atrium and the right ventricle, which helps maintain the physiological relationship between atrial and ventricular contraction, and allows the paced heart to follow the increase in sinus rate which occurs during exercise. The wires in a dual-chamber pacemaker carry pulses between the right atrium (the upper right chamber of your heart) and the right ventricle and the generator. The pulses help coordinate the timing of these two chambers contractions. Dual-chamber pacemakers tend to prevent more subsequent heart problems than single-chamber ventricular pacemakers.

Figure 2.4: Dual chamber pacemaker

This is an extension of the single chamber to dual chamber pacemaker. The basic working principle is the same as single chamber pacemaker. Just that after the pacing of atrium, the state changes to the 'Reset Timer' state of the ventricle and not the 'Reset Timer' state of the atrium. So the general flow of a complete cycle of the pacemaker goes in the following path:

Reset Timer A Wait A Pace A Reset Timer V Wait V Pace V.

Then the process continues in a cyclic manner again. The following is the state diagram. The inputs and outputs hold the same significance; 'a' suffix stands for atria, and 'v'Suffix sands for ventricle.

#### Inputs:

sV: sensing parameter: 1 if contraction is sensed in the ventricle.

**Heart\_beats**: the number of heart beats per minute , 35-55bpm, heart\_beats=1; 65-85bpm, heart\_beats=0; 95-125bpm, heart\_beats=1

#### **Outputs:**

tV: output to timer: 1 if timer for the ventricle is to be reset. pV: output to heart : 1 if pacing needs to be done in the ventricle

Figure 2.5: State diagram of dual chamber pacemaker

# International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Impact Factor (2012): 3.358

|       | Table 3  | State | table of dua | li chai | mber | pacen | naker |     |

|-------|----------|-------|--------------|---------|------|-------|-------|-----|

| State | Function | i/p   | i/p          | o/p     | o/p  | o/p   | o/p   | o/p |

|       |          | sA    | Heart_beat   | sV      | pА   | pV    | tA    | tV  |

| Α     | waitA    | 0     | 0            | х       | 0    | 0     | 0     | 0   |

| В     | paceA    | 0     | 1            | х       | 1    | 0     | 0     | 0   |

| С     | ResetA   | 1     | 0            | х       | 0    | 0     | 1     | 0   |

|       | TimerA   | 1     | 1            | х       | 0    | 0     | 1     | 0   |

| D     | waitA    | Х     | 0            | 0       | 0    | 0     | 0     | 0   |

| Е     | paceA    | Х     | 1            | 0       | 0    | 1     | 0     | 0   |

| F     | ResetA   | Х     | 0            | 1       | 0    | 1     | 0     | 0   |

|       | TimerA   | Х     | 1            | 1       | 0    | 0     | 0     | 1   |

**Table 3**: State table of dual chamber pacemaker

# **3.** Experimental Results

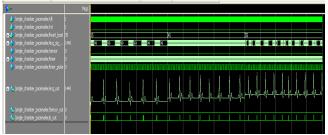

The pacemaker designed in Verilog HDL and verified its Functionality. The syntax of the RTL design is checked using Xilinx tool. The pacemaker design is first simulated in ModelSim, shown in below figure. The design is verified both at a top level. The design has been Synthesized targeting Xilinx FPGA spartan3A (XCS200A -5fg256) device. The device utilization of both the pacemaker is shown in Table-I. The timing delay is also calculated for both the pacemakers, which shows that the single chamber pacemaker is consuming.

## 3.1(A) Bradycardia: rst=0, heart\_beat= 35-55 sensor\_out=0, pacemaker\_out=1.

Figure 3.1(A): Simulation Results of Single chamber pacemaker

# 3.1(B) Normal heart beat: rst=0, heart\_beat= 65-85 sensor\_out=1, pacemaker\_out=0.

Figure 3.1(B): Simulation Results of Single chamber pacemaker

Figure 3.1(C): Simulation Results of Single chamber pacemaker

# 3.2 Dual chamber simulation results

# 3.2(A) CASE 1: sA=1/0, sV=x , pA=1/0, pV=0

(*a*) *Bradycardia:* Rst=0, heart\_beat=35-55bpm, sA=0, pA=1, pV=0.

Figure 3.21: Simulation Results of dual chamber pacemaker

(b) Normal Heart beats: Rst=0, heart\_beat=65-85bpm, sA=1, pA=0,pV=0.

Figure 3.22: Simulation Results of dual chamber pacemaker

| Device      | Available | Singl     | e chamber   | Dual chamber |             |  |

|-------------|-----------|-----------|-------------|--------------|-------------|--|

| utilization |           | pacemaker |             | pacemaker    |             |  |

|             |           | Used      | Utilization | Used         | Utilization |  |

| Number of   | 1792      | 1715      | 95%         | 1685         | 91%         |  |

| Slices      |           |           |             |              |             |  |

| `Number of  | 3584      | 14        | 0%          | 29           | 0%          |  |

| Slice Flip  |           |           |             |              |             |  |

| Flops       |           |           |             |              |             |  |

| Number of   | 3584      | 3202      | 89%         | 3152         | 86%         |  |

| 4 Input     |           |           |             |              |             |  |

| LUTs        |           |           |             |              |             |  |

| Number of   | 68        | 28        | 41%         | 31           | 46%         |  |

| Bonded      |           |           |             |              |             |  |

| IOBs        |           |           |             |              |             |  |

| Number of   | 24        | 1         | 4%          | 3            | 8%          |  |

| GCLKs       |           |           |             |              |             |  |

(c) Tachycardia: Rst=0, heart\_beat=95-125bpm, sA=0, pA=1,pV=0.

Figure 3.23: Simulation Results of dual chamber pacemaker

#### 3.2(B) CASE 2: sA=x, sV=1/0 , pA=0, pV=1/0

(a) Bradycardia: : Rst=0, heart\_beat=35-55bpm, sV=0, pA=0,pV=1.

Figure 3.24: Simulation Results of dual chamber pacemaker

(*b*) Normal Heart beat: heart\_beat=65-85bpm pA=0, pV=0,sA=x, sV= 1, pA=0, pV =1.

Figure 3.25: Simulation Results of dual chamber pacemaker

(c) Tachycardia: Rst=0, heart\_beat=95-125bpm, sV=0, pA=0,pV=1.

Figure 3.26: Simulation Results of dual chamber pacemaker

3.3 Device utilization of single and dual chamber pacemaker

3.4 Timing analysis of single and dual chamber pacemaker

| Time & Frequency      | Single Chamber | Dual Chamber |  |

|-----------------------|----------------|--------------|--|

| Analysis              | Pacemaker      | Pacemaker    |  |

| Minimum Period        | 3.867ns        | 3.842ns      |  |

| Maximum Frequency     | 258.632mhz     | 260.276mhz   |  |

| Minimum Input Arrival | 2.109ns        | 12.309ns     |  |

| Time Before Clock     |                |              |  |

| Maximum Output        | 21.241ns       | 15.225ns     |  |

| Required Time After   |                |              |  |

| Clock                 |                |              |  |

3.5 Power analysis of single and dual chamber pacemaker

| Supply Power | Single Chamber | Dual Chamber |

|--------------|----------------|--------------|

|              | Pacemaker      | Pacemaker    |

| Dynamic      | 0.001          | 0.004        |

| Quiesent     | 0.022          | 0.021        |

| Total        | 0.023          | 0.025        |

# 4. Conclusion

The single and dual chamber pacemaker is designed in verilog-HDL. The Simulation is done with Modelsim simulator and also implemented on Xilinx FPGA Spartan 3A(XC3S200A-5FG256).The Simulation & implementation results show that the designed pacemaker is working properly with all the heart beats from 35-125bpm.

# 5. Future Scope

Single and dual chamber pacemaker can be implemented to verify various modes like VVI mode, DDI mode and DDTR mode.

# 6. Acknowledgement

The authors would like to thank Nitte Meenakshi Institute of Technology for providing the lab time and resources and the necessary support and coordination.

# References

- [1] WILLIAM BATSFORD "Pacemakers and Antitachycardia Devices" M.D.chapter 26

- [2] Lise M. Stevens "Heart pacemakers" article in the journal of the American medical association.

- [3] Brendan Phibbs, The Human Heart, 3rd ed., St. Louis: The C. V. Mosby Company, 1975

- [4] Daniel Halperin , Thomas S. Heydt-Benjamin, Benjamin Ransford Shane S. Clark"Journal article: Pacemakers and implantable cardiac defibrillators:"

- [5] Jason McMullan, Matthew Valento, Mehran Attari, Arvind Venkat "Review article: Care of the pacemaker/implantable cardioverter defibrillator patient in the ED (emergency department.)"

International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Impact Factor (2012): 3.358

- [6] Taolue Chen Marco Diciolla Marta Kwiatkowska Alexandru Mereacre "Quantitative Verification of Implantable Cardiac Pacemakers"

- [7] Daniel Halperin, Thomas S. Heydt-Benjamin, Benjamin Ransford ,Shane S. Clark, Benessa Defend, Will Morgan, Kevin Fu, Tadayoshi Kohno, William H. Maisel, MD, "Pacemakers and Implantable Cardiac Defibrillators:Software Radio Attacks and Zero-Power Defenses" This paper, copyright the IEEE, will appear in the proceedings of the 2008 IEEE Symposium on Security and Privacy.

- [8] Manoj Kollam, supraja pranesh, Anitha Raghavendra "Vlsi implementation of demand mode dual chamber cardiac pacemaker" International Journal of Engineering and Innovative Technology(IJEIT) volume2, issue 4, october 2012

- [9] J.Lasa, M.Mguez, A.Amaud "Complete integrated Cardiac Sensing Channel for Pacemaker" 2012 Argentine school of Micro-nanoelectronics, technology and application

- [10] Silveria, Denis Flandre ". A 110na pacemaker sensing channel in cmos on silicon on insulator Fernado"

- [11]Salim AL-Ahdab, Reza Lotfi and Wouter A.Serdijin "A 1v 225nW 1KS/s current successive approximation ADC for pacemakers" Biomedical electronics group, Electronic research laboratory, the Netherlands.

- [12] George Major Chen, *FellowZhihao Jiang*, Rahul Mangharam, "Model-Based Conformance Testing for Implantable Pacemakers" University of Pennsylvania

- [13] Manoj Kollam, Supraja Pranesh, Anitha Raghavendra "Implementation of a Demand Mode Responsive Cardiac Pacemaker" International Journal of Engineering and Innovative Technology (IJEIT) Volume 2, Issue 4, October 2012

- [14] Wei Vivien Shi, Timothy N. Chang, and MengChu Zhou "Method to Detect Cardiac Abnormalities Based on Electrocardiography and Sinoatrial Pacemaker Model" Proceedings of the 2010 IEEE, International Conference on Mechatronics and Automation, August 4-7, 2010, Xi'an, China

- [15] M. Daliri, M. Maymandi-Nejad "A 0.8-V 420nW CMOS Switched-Opamp Switched-Capacitor Pacemaker Front-End With a New Continuous-Time CMFB" IEEE Xplore 2009.

- [16] Amandeep Kaur "Analysis of VLSI Pacemaker Designs: A review" International Journal on Recent and Innovation Trends in Computing and Communication ISSN: 2321-8169 Volume: 2 Issue: 4.

- [17] Santosh Chede and Kishore Kulat "Design Overview Of Processor Based Implantable Pacemaker" JOURNAL OF COMPUTERS, VOL. 3, NO. 8, AUGUST 2008.

- [18] Enes Elvin Gul and Mehmet Kayrak "Common Pacemaker Problems: Lead and Pocket Complications" www.intechopen.com

Kiran Kumar Jembula , Prof. G.Srinivasulu, Dr. Prasad

K.S "Design Of Electrocardiogram (ECG Or EKG) System On FPGA" Research Inventy: International Journal Of Engineering And Science Vol.3, Issue 2 (May 2013), PP 21-27

- [19] S.Karpagachelvi, Dr.M.Arthanari, Prof. & Head, M.Sivakumar, "ECG Feature Extraction Techniques - A Survey Approach" (IJCSIS) International Journal of

Computer Science and Information Security, Vol. 8, No. 1, April 2010.

[20] Patrick E. McSharry, Gari D. Clifford, Lionel Tarassenko, and Leonard A. Smith "A Dynamical Model for Generating Synthetic Electrocardiogram Signals" IEEE TRANSACTIONS ON BIOMEDICAL ENGINEERING, VOL. 50, NO. 3, MARCH 2003

## **Author Profile**

**Roopa T** received her Bachelor of Engineering degree from University Visvesvaraya College of Engineering, Bangalore, Karnataka, in the year 2009. She is currently pursuing Master of Technology in Nitte Meenakshi Institute of Technology, Bangalore;

affiliated to Vishweshwaraiah Technological University, Belgaum. Her research of interest is VLSI.

**Mrs. Manjula B.M.** graduated from Mangalore University in 2000. She has completed her M. Tech. in 2007 from Vishweshwaraiah Technological University, Belgaum and currently working as an Asst. Professor in ECE Dept, Nitte Meenakshi Institute of

Technology, Yelahanka, Bangalore. Her research interest is Biomedical Signal Processing.

**Dr. Chirag Sharma** graduated from Maharaja Sayajirao University, Vadodara, in June 2001. He has completed his M.S at Utah State University, USA in 2003 and Ph.D., from University of Utah in 2009. He Worked as Staff Design Engineer at Cypress

Semiconductors, USA. Currently he is working as Professor in ECE Dept, Nitte Meenakshi Institute of Technology, Yelahanka, Bangalore. His research interests include low-power and Fault-Tolerant VLSI Design.