# Matlab Simulink Modeling of Hybrid Cascaded Five Level Inverter

### T. Murali Krishna

<sup>1</sup>Assitant Professor, Dept. of EEE, CBIT, Gandipet, Hyderabad, Telangana, India

**Abstract:** Multi Level Inverters (MLI) are drawing more importance in medium power and medium voltage ac drive applications. In the design of multi level inverters, different topologies have been evolved. In order to minimize the required elements and to reduce the switching losses, hybrid topologies are upcoming. This paper presents the detailed modeling and operation of Hybrid-cascaded multi level inverter topology. The modeling is performed in MATLAB Simulink environment.

Keywords: Multi level inverters, topologies, modeling, MATLAB-Simulink

## 1. Introduction

The conventional two-level inverters are getting obsolete for the industrial drive applications because of their disadvantages like i) requirement of more switching elements ii) additional switching losses iii) bulky driver circuit requirements iv) high dv/dt problems etc[1]. As a solution to the above problems multi level inverters are emerged with different topologies[2]. The foremost traditional topologies are diode clamped, flying capacitor and cascaded H-bridge[3]. But out of these three topologies diode clamped and cascaded H-bridge topologies have developed into eminent for various applications[4]. The diode clamped topology requires only one dc source and different voltage levels can be obtained by connecting various capacitors in series which creates voltage balancing problem[5]. Whereas the cascaded topology requires several dc sources which reduces the complexity of design. The key disadvantages of flying capacitor topology are voltage balancing and control circuit complexity. Hence different combinations of basic topologies have been tried, which has become a curtain raiser to hybrid topologies[6].

## 2. Structure of Hybrid Cascaded MLI

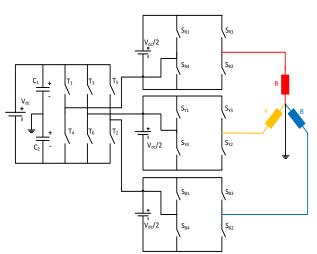

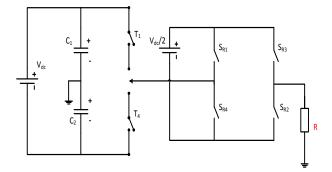

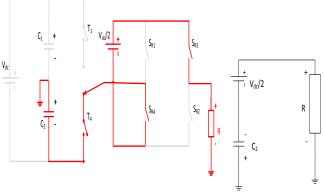

Hybrid topologies are the latest structures, where the cascaded series inverters have distinct internal dc bus voltages, use different switching devices and/or modulated quite differently[7]. The significant feature of the proposed multilevel inverter topology is the reduction of switches and consequently minimizing the switching losses[8][9]. The structure of Hybrid cascaded MLI is represented in the figure 1. The bottom one is of a standard 3-leg inverter with a dc power source and the top is an H-bridge in series with each standard inverter leg. The H-bridge can use a capacitor, battery or other dc power source like PV array. The single phase representation of Hybrid cascaded MLI is shown in figure 2. The neutral point is taken as the output phase voltage reference point for understanding its working. There are six switch combinations to produce different five-level voltages across the load.

Figure 1: Three phase structure of hybrid cascaded MLI

Figure 2: Single phase structure of hybrid cascaded MLI

The sequence of the switches operating to provide different voltage levels is clearly shown from figure 3 to figure8. The five voltage levels are V,V/2,0,-V/2 and V. To get output voltage of level V, the switches  $T_1$ ,  $S_{R3}$  and  $S_{R4}$  must be closed where as the remaining switches must be in OFF state.

Then the voltage across  $C_1$  (V/2) in the standard 3 leg inverter is added to the voltage source (V/2) at the top H-bridge inverter to provide an output voltage of V which is shown in figure 3.

Figure 3: Circuit operation for output voltage V

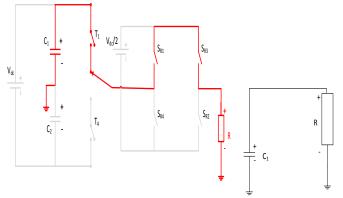

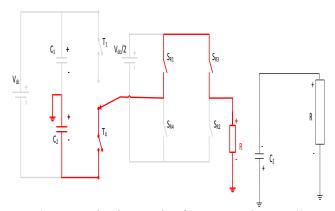

To get an output voltage of V/2, then switch OFF  $S_{R4}$  and switch ON  $S_{R1}$ . Then the voltage supplied by the top inverter will become zero. Hence the voltage across  $C_1$  alone appears across the load. The equivalent circuit is shown in figure 4.

Figure 4: Circuit operation for output voltage V/2

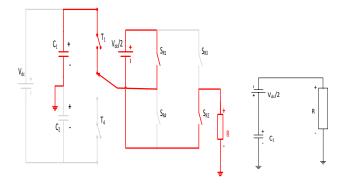

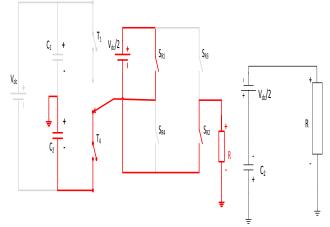

For providing zero output voltage there are two possible switching states. First one is switch OFF  $S_{R3}$  and switch ON  $S_{R2}$ . The second one is the complement of the above switching state i.e.  $T_1$  is OFF  $T_4$  is ON,  $SR_1$   $SR_2$  are OFF and  $S_{R3}$ ,  $S_{R4}$  are ON. The circuit equivalent for these switching states is depicted in figures 5 and 6. In this state the voltage across  $C_1$  or C2 is opposed by the top voltage source results an output voltage of zero.

Figure 5: Circuit operation for output voltage 0

Figure 6: Circuit operation for output voltage 0

The output voltage can be made -V/2 by operating the switches  $T_4$ ,  $S_{R1}$  and  $S_{R3}$  in ON state. The voltage supplied by the top inverter will be zero. Therefore the voltage across  $C_2$  will only appear across the load which is shown in figure 7.

Figure 7: Circuit operation for output voltage -V/2

Figure 8: Circuit operation for output voltage -V

In order to get the output voltage -V, the voltage across  $C_2$  must be added with the top inverter voltage source value by keeping  $T_4$  ON, switching OFF  $S_{R3}$  and switch ON  $S_{R2}$ . The corresponding equivalent circuit is shown in figure 8. The switching states required for the operation of Hybrid cascaded five level inverter are summarized and given in the table1.

## International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064 Index Copernicus Value (2013): 6.14 | Impact Factor (2014): 5.611

| Table 1. Switching states for Hybrid caseaded WEI |                  |                |          |                            |                 |                            |

|---------------------------------------------------|------------------|----------------|----------|----------------------------|-----------------|----------------------------|

|                                                   | Switching States |                |          |                            |                 |                            |

| Voltage<br>levels                                 | T <sub>1</sub>   | T <sub>4</sub> | $S_{R1}$ | $\mathbf{S}_{\mathrm{R2}}$ | S <sub>R3</sub> | $\mathbf{S}_{\mathrm{R4}}$ |

| $+V_{dc}$                                         | 1                | 0              | 0        | 0                          | 1               | 1                          |

| $+V_{dc}/2$                                       | 1                | 0              | 1        | 0                          | 1               | 0                          |

| 0                                                 | 1                | 0              | 1        | 1                          | 0               | 0                          |

|                                                   | 0                | 1              | 0        | 0                          | 1               | 1                          |

| -V <sub>dc</sub> /2                               | 0                | 1              | 1        | 0                          | 1               | 0                          |

| -V <sub>dc</sub>                                  | 0                | 1              | 1        | 1                          | 0               | 0                          |

## Table 1: Switching states for Hybrid cascaded MLI

## 3. Simulation of Hybrid 5-level MLI

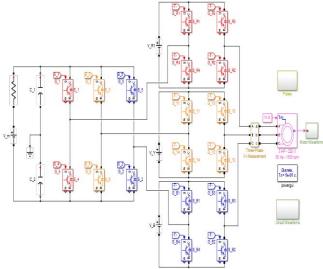

The MATLAB-Simulink simulation diagram is shown in figure 9.

Figure 9: Simulink diagram of Hybrid cascaded MLI

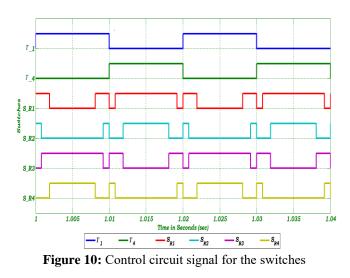

The control signals from the driver circuit are shown in figure 10. The switches  $T_1$  and  $T_4$  are complementary to each other. Whereas  $S_{R1}$  &  $S_{R4}$ ,  $S_{R2}$  &  $S_{R3}$  are complementary to each other.

4. Results

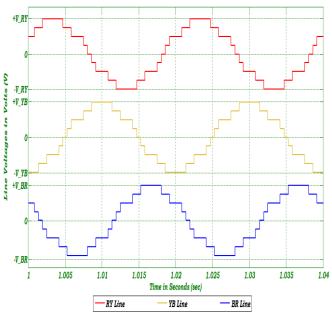

Figure 13: Output Line Voltages

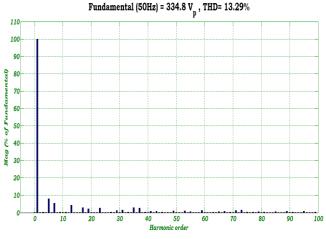

Figure 14: Frequency Spectrum of Line Voltage

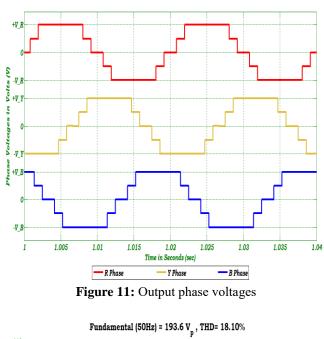

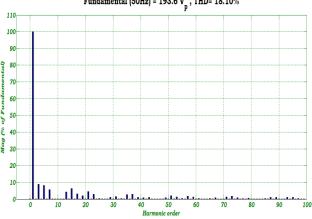

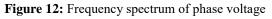

The output phase voltages with resistive load are shown in figure 11. The voltages are of same magnitude but displaced each other by 120 degrees. The frequency spectrum of the phase voltage is given in figure 12. It is observed that 3<sup>rd</sup>, 5<sup>th</sup>, 7<sup>th</sup>, 13<sup>th</sup>, 15<sup>th</sup>, 17<sup>th</sup>, 21<sup>th</sup> harmonics are predominant in each phase voltage. The line to line voltage contains 9 levels in its waveform. The line to line voltage waveforms are shown in figure 13. The frequency spectrum of line to line voltages is depicted in figure 14. From the frequency spectrum of line to line voltage are absent. In line to line voltage waveform 5<sup>th</sup>, 7<sup>th</sup>, 13<sup>th</sup>, 17<sup>th</sup> and 19<sup>th</sup> harmonics are most predominant.

## 5. Conclusion

From the above results and discussion it can be concluded that the Hybrid cascaded MLI requires less number of elements per phase to produce a five level voltage output. The work can be extended to different pulse width modulation techniques to reduce the dominant harmonics.

## References

- L. G. Franquelo, J. L. Rodriguez, J. Leon, S. Kouro, R. Portillo, and M. A. Prats, " The age of multilevel converters arrives," *IEEE Ind. Electron. Mag.*, vol.2, no. 2, pp. 28-39, Jun. 2008.

- [2] M. Zahra, M. Jafari, Md. R. Islam and J. Zhu, "A comparative study on characteristics of major topologies of voltage source multilevel inverters," *IEEE Innovative Smart Grid Tech.*, pp. 612-617, 2014.

- [3] J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt and S. Kouro, "Multilevel voltage-source-converter topologies for industrial medium-voltage drives," *IEEE Trans. Ind. Electro.*, vol. 54, no. 6, pp. 2930-2945, Dec. 2007.

- [4] K. A. Corzine, M. W. Wielebski, F. Z. Peng, and J. Wang, "Control of Cascaded Multilevel Inverters," *IEEE Trans. power electron*, vol. 19, no. 3, pp. 732-738, May 2004.

- [5] M. Marchesoni and P. Tenca, "Diode-Clamped multilevel converters: A practicable way to balance dclink voltages," *IEEE Trans. Ind. Electron.*, Vol. 49, no. 4, pp. 752-765, Aug. 2002.

- [6] P. Thongprasri, "A 5-level three-phase cascaded hybrid multilevel inverter," *IJCEE*, vol. 3, no. 6, pp. 789-794, Dec. 2011.

- [7] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium-voltage multilevel converters - state of the art, challenges, and requirements in industrial application," *IEEE Trans. Ind. Electr.* vol. 57, no. 8, pp. 2581-2596, Aug. 2010.

- [8] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," *IEEE Trans. Ind. Electro*, vol. 49, no. 4, pp. 724-738, Aug. 2002.

- [9] E. Najafi, and A. H. Md. Yatim, "Design and implementation of a new multilevel inverter topology," *IEEE Trans. Ind. Electr.* vol. 59, no. 11, pp. 4148-4154, Nov. 2012.

## **Author Profile**

**T. Murali Krishna** received M.Tech degree from JNTU Hyderabad in 2005. Presently working as Assistant Professor in the Department of EEE, Chaitanya Bharathi Institute of Technology, Hyderabad for the last 8 years, having 15 years of

experience in teaching. He published 13 papers in various international journals and conferences. His areas of interest include power electronics, FACTS, wavelets and power quality.

#### Volume 4 Issue 12, December 2015 <u>www.ijsr.net</u> Licensed Under Creative Commons Attribution CC BY